Intel 386 User Manual

Page 640

E-3

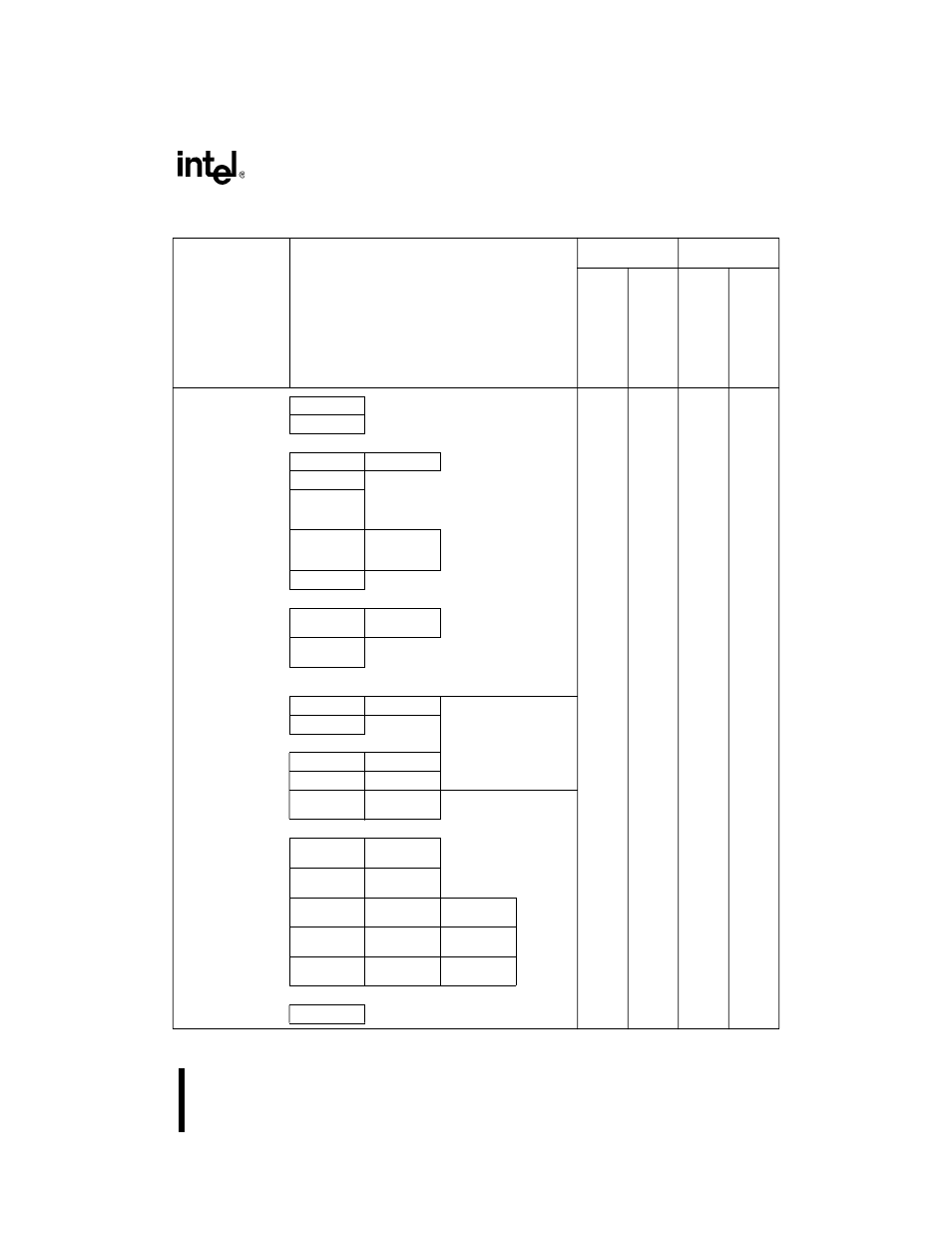

INSTRUCTION SET SUMMARY

immediate

0 1 1 0 1 0 s 0

immediate data

2

4

b

h

PUSHA = Push All

0 1 1 0 0 0 0 0

18

34

b

h

POP = Pop

register/memory

1 0 0 0 1 1 1 1

mod 0 0 0 r/m

5/7

7/9

b

h

register (short form)

0 1 0 1 1 reg

6

6

b

h

segment register (ES,

CS, SS, or DS)

(short form)

000 sreg2 111

7

25

b

h, i, j

segment register (ES,

CS, SS, or DS) FS or

GS

0 0 0 0 1 1 1 1

10 sreg3 001

7

25

b

h, i, j

POPA = Pop all

0 1 1 0 0 0 0 1

29

35

b

h

XCHG = Exchange

register/memory

with register

1 0 0 0 0 1 1 w

mod reg r/m

3/5**

3/5**

b, f

f, h

register with accumula-

tor (short form)

1 0 0 1 0 reg

3

3

IN = Input from

Clk Count Virtual

8086 Mode

fixed port

1 1 1 0 0 1 0 w

port number

†27

14*

8*/29*

s/t, m

variable port

1 1 1 0 1 1 0 w

†28

15*

9*/29*

s/t, m

OUT = Output to

fixed port

1 1 1 0 0 1 1 w

port number

†27

14*

8*/29*

s/t, m

variable port

1 1 1 0 1 1 1 w

†28

15*

9*/29*

s/t, m

LEA = Load EA to regis-

ter

1 0 0 0 1 1 0 1

mod reg r/m

2

2

SEGMENT CONTROL

LDS = Load pointer to

DS

1 1 0 0 0 1 0 1

mod reg r/m

7*

26*/28*

b

h, i, j

LES = Load pointer to

ES

1 1 0 0 0 1 0 0

mod reg r/m

7*

26*/28*

b

h, i, j

LFS = Load pointer to

FS

0 0 0 0 1 1 1 1

1 0 1 1 0 1 0 0

mod reg r/m

7*

29*/31*

b

h, i, j

LGS = Load pointer to

GS

0 0 0 0 1 1 1 1

1 0 1 1 0 1 0 1

mod reg r/m

7*

26*/28*

b

h, i, j

LSS = Load pointer to

SS

0 0 0 0 1 1 1 1

1 0 1 1 0 0 1 0

mod reg r/m

7*

26*/28*

b

h, i, j

FLAG CONTROL

CLC = Clear carry flag

1 1 1 1 1 0 0 0

2

2

Table E-1. Instruction Set Summary (Sheet 2 of 19)

Instruction

Format

Clock Count

Notes

Real

Ad-

dress

Mode

or

Virtual

8086

Mode

Pro-

tected

Virtual

Ad-

dress

Mode

Real

Ad-

dress

Mode

or

Virtual

8086

Mode

Pro-

tected

Virtual

Ad-

dress

Mode