7 peripheral register addresses, Table 42. peripheral register addresses (sheet 6 – Intel 386 User Manual

Page 66

4-15

SYSTEM REGISTER ORGANIZATION

4.7

PERIPHERAL REGISTER ADDRESSES

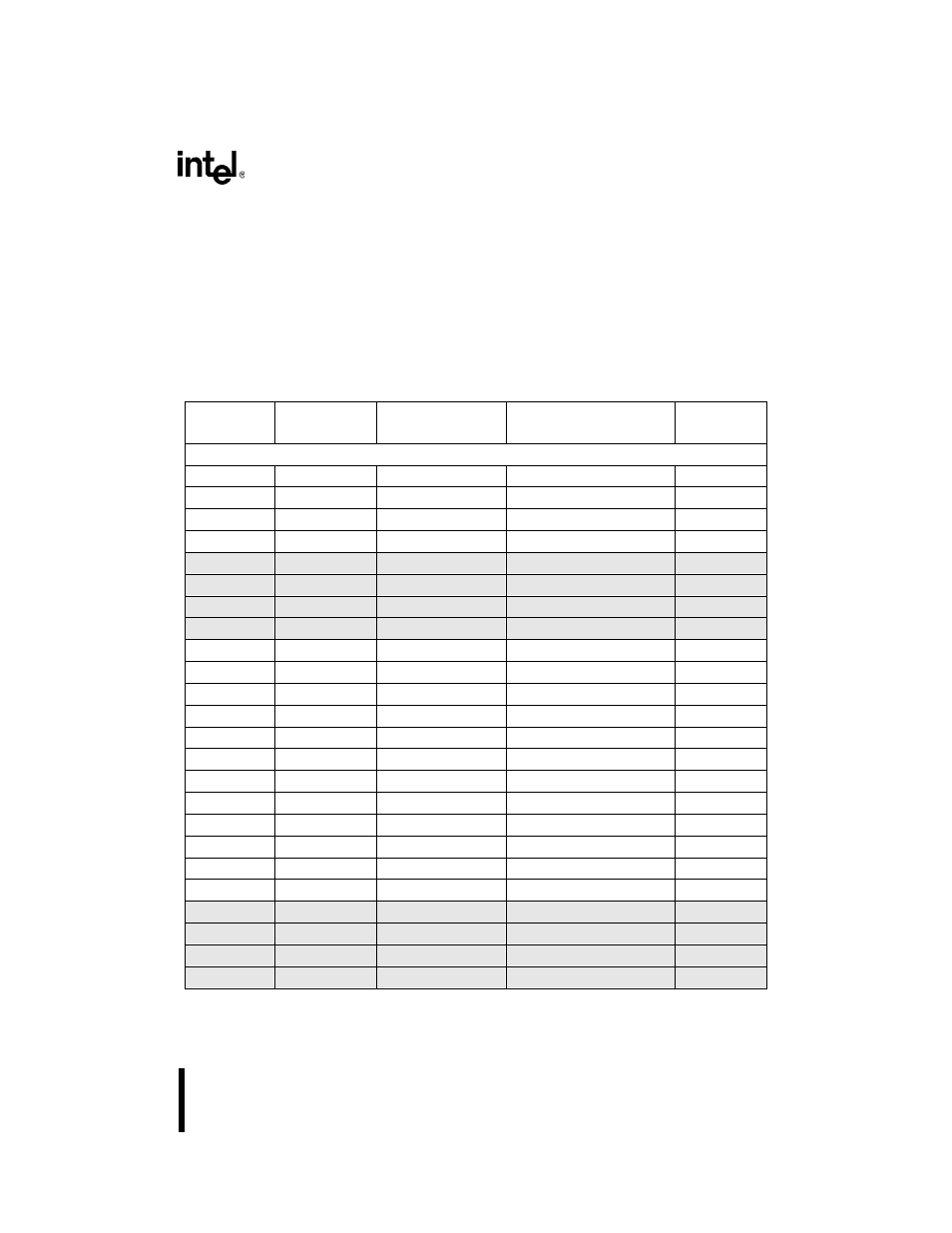

Table 4-2 lists the addresses and names of all user-accessible peripheral registers. I/O Registers

can be accessed as bytes or words. Word accesses to byte registers result in two sequential 8-bit

I/O transfers. The default (reset) value of each register is shown in the Reset Value column. An X

in this column signifies that the register bits are undefined. Some address values do not access

registers, but are decoded to provide a logic control signal. These addresses are listed as Not a

register in the Reset column.

Table 4-2. Peripheral Register Addresses (Sheet 1 of 6)

Expanded

Address

PC/AT

Address

Access Type

(Byte/Word)

Register Name

Reset Value

DMA Controller and Bus Arbiter

F000H

0000H

Byte

DMA0TAR0/1 (Note 1)

XX

F001H

0001H

Byte

DMA0BYC0/1 (Note 1)

XX

F002H

0002H

Byte

DMA1TAR0/1 (Note 1)

XX

F003H

0003H

Byte

DMA1BYC0/1 (Note 1)

XX

F004H

0004H

Reserved

F005H

0005H

Reserved

F006H

0006H

Reserved

F007H

0007H

Reserved

F008H

0008H

Byte

DMACMD1/DMASTS

00H

F009H

0009H

Byte

DMASRR

00H

F00AH

000AH

Byte

DMAMSK

04H

F00BH

000BH

Byte

DMAMOD1

00H

F00CH

000CH

Byte

DMACLRBP

Not a register

F00DH

000DH

Byte

DMACLR

Not a register

F00EH

000EH

Byte

DMACLRMSK

Not a register

F00FH

000FH

Byte

DMAGRPMSK

03H

F010H

Byte

DMA0REQ0/1

XX

F011H

Byte

DMA0REQ2/3

XX

F012H

Byte

DMA1REQ0/1

XX

F013H

Byte

DMA1REQ2/3

XX

F014H

Reserved

F015H

Reserved

F016H

Reserved

F017H

Reserved

NOTES:

1.

Byte pointer in flip-flop in DMA determines which register is accessed.

2.

Shaded rows indicate reserved areas.