7 command 2 register (dmacmd2), Figure 1224. dma command 2 register (dmacmd2), Figure 12-24) – Intel 386 User Manual

Page 372

12-37

DMA CONTROLLER

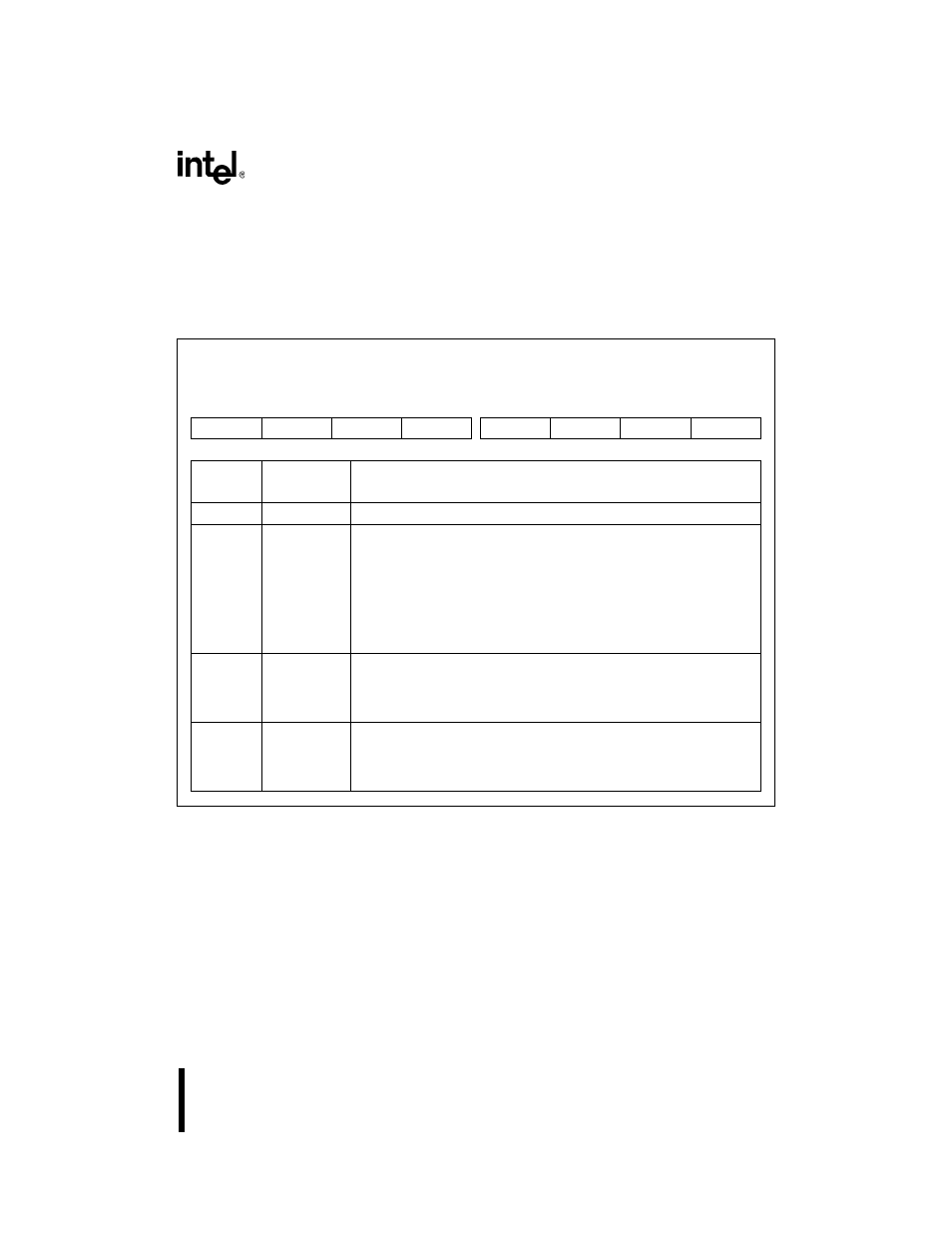

12.3.7 Command 2 Register (DMACMD2)

Use DMACMD2 to select the DREQn and EOP# sampling: asynchronous or synchronous. Bus

timing diagrams that show the differences between asynchronous and synchronous sampling are

shown in Figure 12-5 on page 12-10 and Figure 12-13 on page 12-21. Also, use DMACMD2 to

assign a particular bus request to the lowest priority level for fixed priority mode.

Figure 12-24. DMA Command 2 Register (DMACMD2)

DMA Command 2

DMACMD2

(write only)

Expanded Addr:

ISA Addr:

Reset State:

F01AH

—

08H

7

0

—

—

—

—

PL1

PL0

ES

DS

Bit

Number

Bit

Mnemonic

Function

7–4

—

Reserved; for compatibility with future devices, write zeros to these bits.

3–2

PL1:0

Low Priority Level Set:

Use these bits to assign a particular bus request to the lowest priority

level in fixed priority mode.

00 =

Assigns channel 0’s request (DREQ0) to the lowest priority level

01 =

Assigns channel 1’s request (DREQ1) to the lowest priority level

10 =

Assigns the external bus master request (HOLD) to the lowest

priority level

11 =

Reserved

1

ES

EOP# Sampling:

0 = Causes the DMA to sample the EOP# input asynchronously.

1 = Causes the DMA to sample the end-of-process (EOP#) input

synchronously.

0

DS

DREQ

n Sampling:

0 = Causes the DMA to sample the DREQ

n inputs asynchronously.

1 = Causes the DMA to sample the channel request (DREQ

n) inputs

synchronously.