4 transmit buffer register (tbrn), Figure 1113. transmit buffer register (tbrn) – Intel 386 User Manual

Page 310

11-23

ASYNCHRONOUS SERIAL I/O UNIT

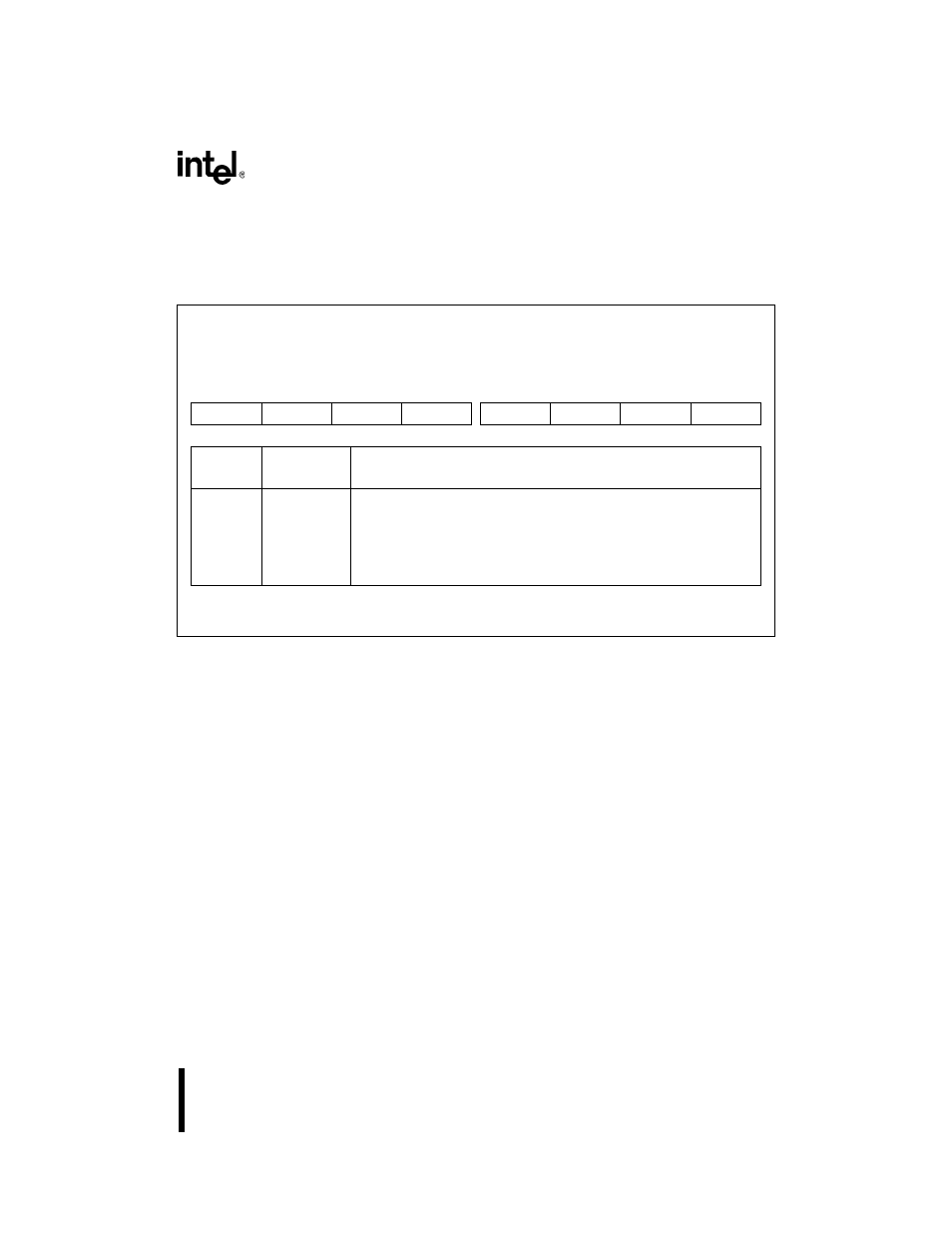

11.3.4 Transmit Buffer Register (TBR

n)

Write the data words to be transmitted to TBRn. Use the interrupt control or DMA units or poll

the serial line status register (LSRn) to determine whether the transmit buffer is empty.

Figure 11-13. Transmit Buffer Register (TBR

n

)

Transmit Buffer

TBR0, TBR1

(write only)

Expanded Addr:

ISA Addr:

Reset State:

TBR0

TBR1

F4F8H

F8F8H

03F8H

02F8H

XXH

XXH

7

0

TB7

TB6

TB5

TB4

TB3

TB2

TB1

TB0

Bit

Number

Bit

Mnemonic

Function

7–0

TB7:0

Transmit Buffer Bits:

These bits make up the next data word to be transmitted. The transmitter

loads this word into the transmit shift register. The transmit shift register

then shifts the bits out, along with the asynchronous communication bits

(start, stop, and parity). The data bits are shifted out least-significant bit

(TB0) first.

NOTE:

The transmit buffer register shares an address port with other SIO registers. You must clear

bit 7 (DLAB) of LCR

n before you can write to the transmit buffer register.