E.2.2 encoding of instruction fields, E.2.2.1 encoding of operand length (w) field, E.2.2.2 encoding of the general register (reg) fie – Intel 386 User Manual

Page 661: Table e3. encoding of operand length (w) field, Table e4. encoding of reg field when w field is n

Intel386™ EX EMBEDDED MICROPROCESSOR USER’S MANUAL

E-24

Unless specified otherwise, instructions with 8-bit and 16-bit operands do not affect the contents

of the high-order bits of the extended registers.

E.2.2

Encoding of Instruction Fields

Within the instruction are several fields indicating register selection, addressing mode, and so on.

The exact encodings of these fields are defined in the next several section.

E.2.2.1

Encoding of Operand Length (w) Field

For any given instruction performing a data operation, the instruction is executing as a 32-bit op-

eration or a 16-bit operation. Within the constraints of the operation size, the w field encodes the

operand size as either one byte or the full operation size, as shown in Table E-3.

E.2.2.2

Encoding of the General Register (reg) Field

The general register is specified by the reg field, which may appear in the primary opcode bytes,

or as the reg field of the “mod r/m” byte, or as the r/m field of the “mod r/m” byte.

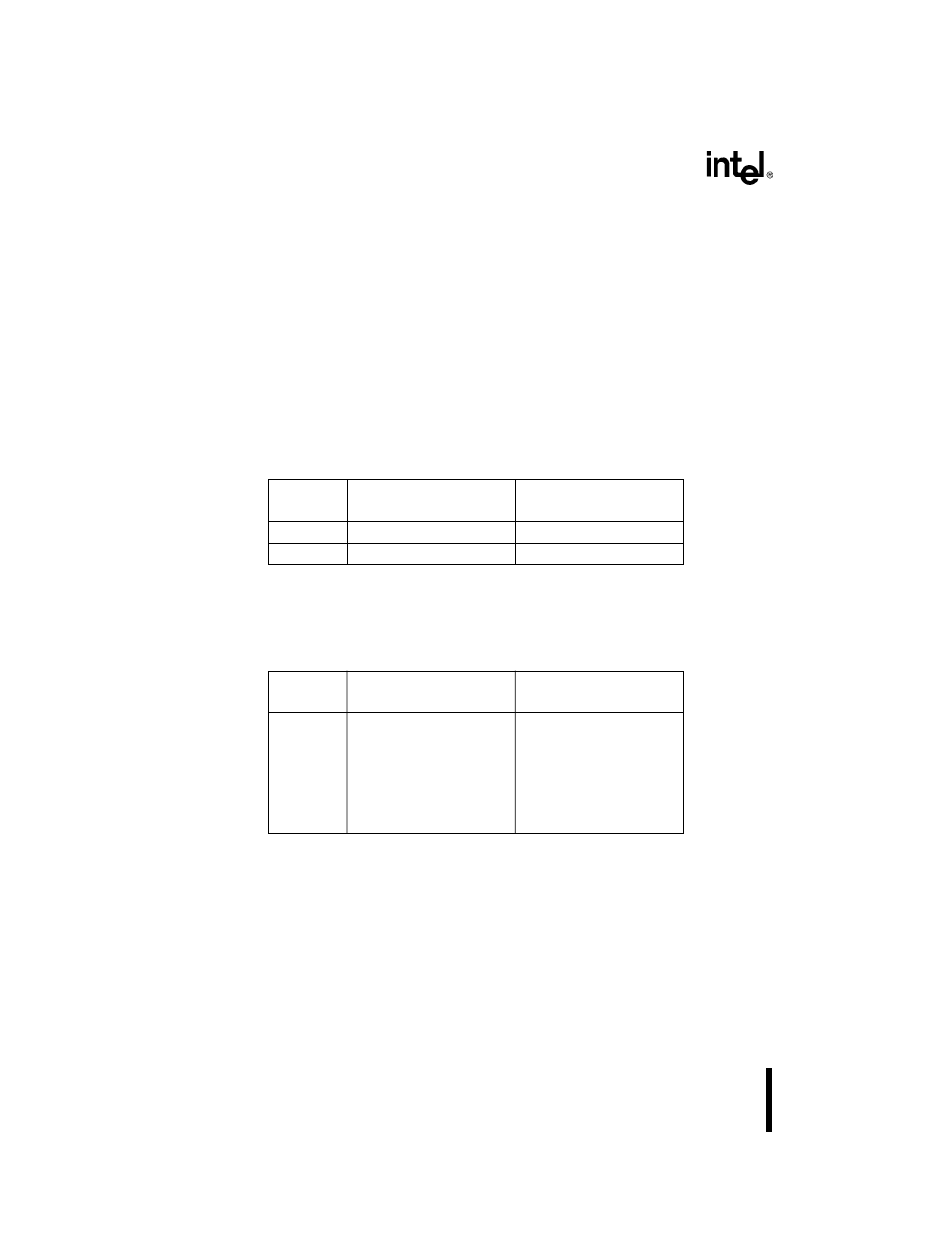

Table E-3. Encoding of Operand Length (w) Field

w Field

Operand Size During 16-bit

Data Operations

Operand Size During 32-bit

Data Operations

0

8 bits

8 bits

1

16 bits

32 bits

Table E-4. Encoding of reg Field When w Field is not Present in Instruction

reg Field

Register Selected During

16-bit Data Operations

Register Selected During

32-bit Data Operations

000

001

010

011

100

101

110

111

AX

CX

DX

BX

SP

BP

SI

DI

EAX

ECX

EDX

EBX

ESP

EBP

ESI

EDI