Chapter 5 systemverilog axi3 and axi4 monitor bfms, Inline monitor connection, Figure 5-1. inline monitor connection diagram – Altera Mentor Verification IP Altera Edition AMBA AXI3/4TM User Manual

Page 121

Mentor VIP AE AXI3/4 User Guide, V10.2b

103

September 2013

Chapter 5

SystemVerilog AXI3 and AXI4 Monitor BFMs

This section provides information about the SystemVerilog AXI3 and AXI4 monitor BFMs.

Each BFM has an API that contains tasks and functions to configure the BFM and to access the

dynamic

during the lifetime of a transaction.

Note

Due to AXI3 protocol specification changes, for some BFM tasks, you reference the

AXI3 interface by specifying AXI instead of AXI3.

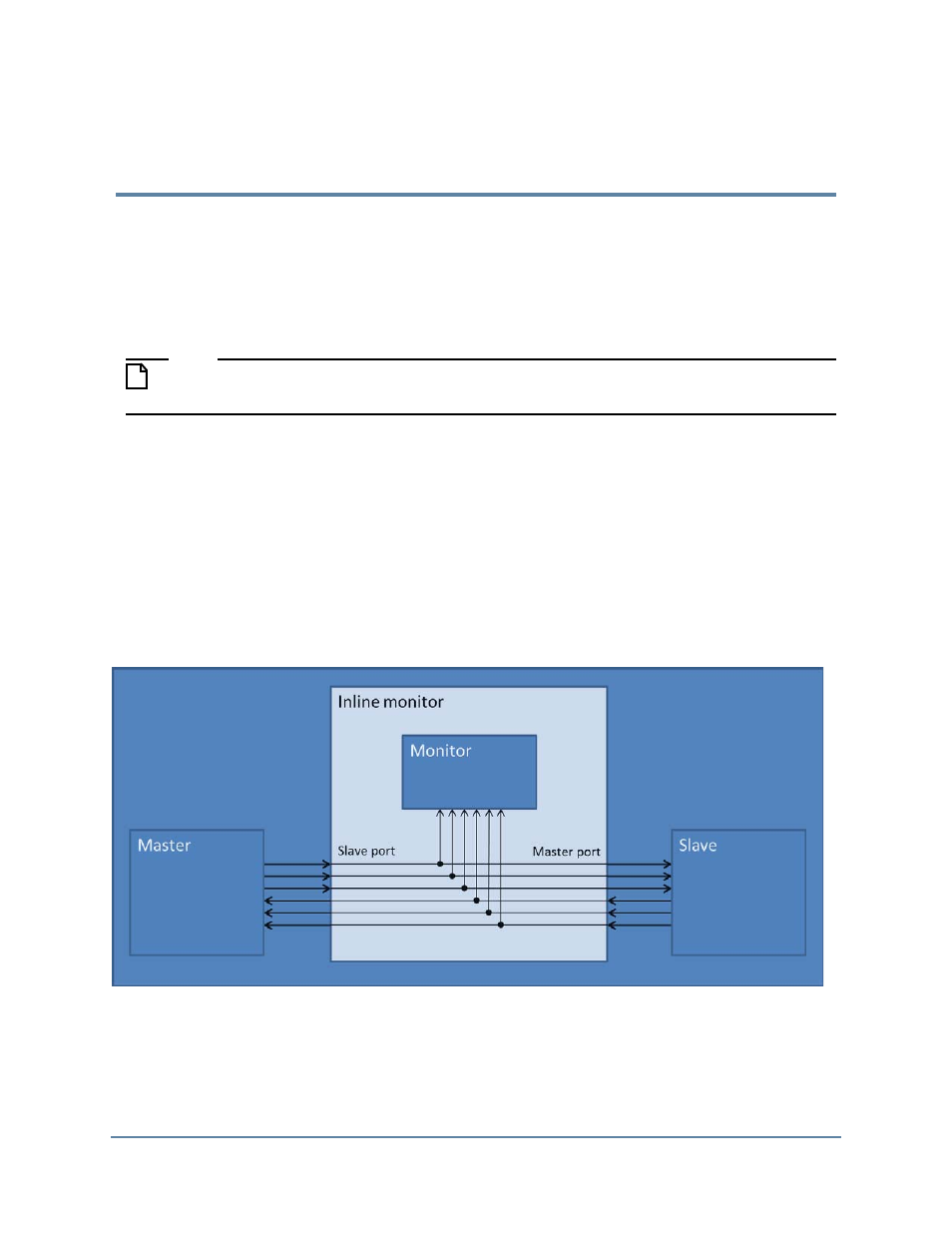

Inline Monitor Connection

The connection of a monitor BFM to a test environment differs from that of a master and slave

BFM. It is wrapped in an inline monitor interface and connected inline between a master and

slave, as shown in

. It has separate master and slave ports and monitors protocol

traffic between a master and slave. The monitor itself then has access to all the facilities

provided by the monitor BFM.

Figure 5-1. Inline Monitor Connection Diagram