Programming – Rockwell Automation 1761 MicroLogix 1000 Programmable Controllers User Manual

Page 231

Using High-Speed Counter Instructions

12–17

An underflow occurs when the hardware accumulator transitions from –32,768 to

+

32,767. When an underflow occurs, the:

•

UN bit is set.

•

High-speed counter interrupt file (program file 4) is executed if the interrupt is

enabled. The IN bit is set and the IH, IL, and IV bits are reset.

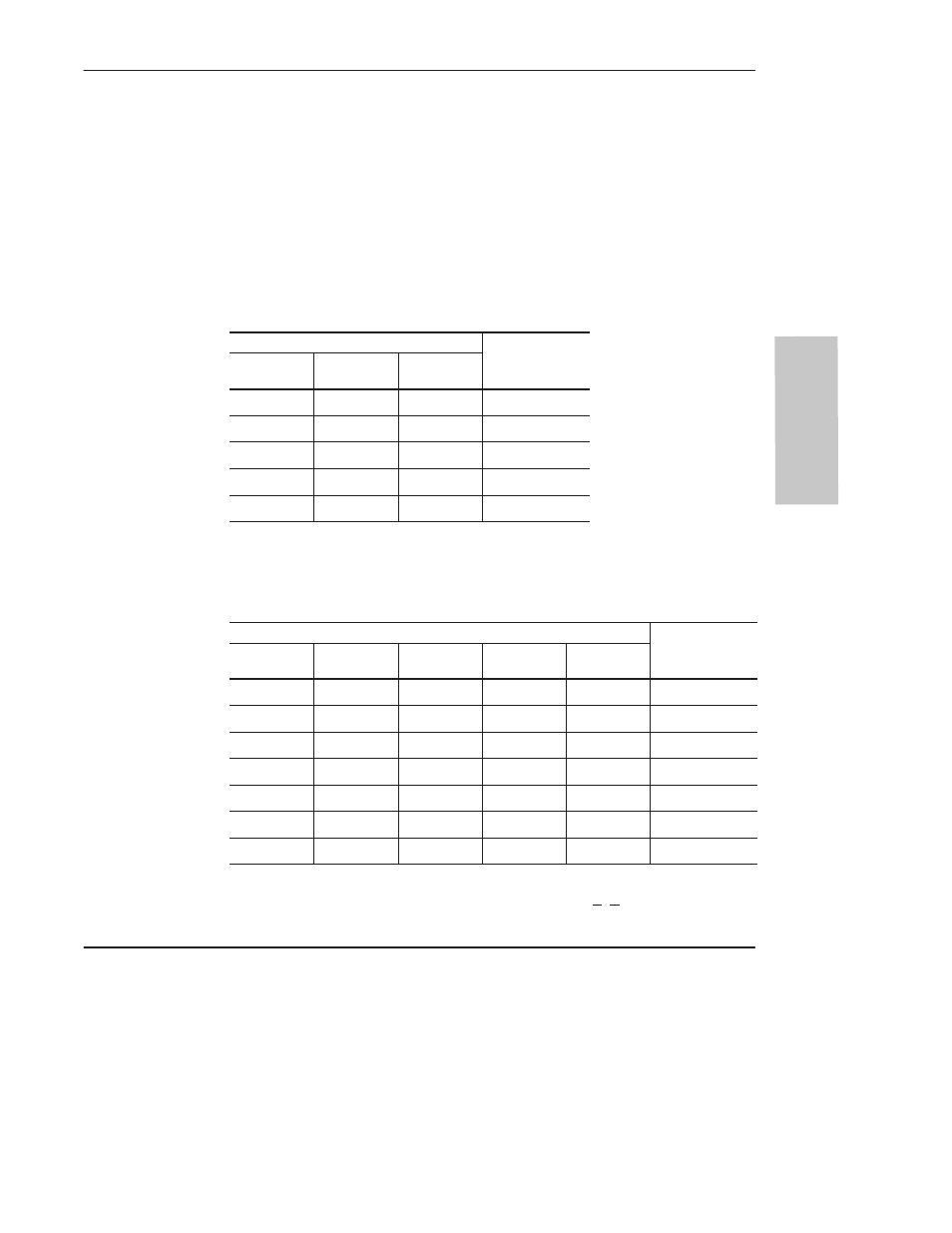

The following tables summarize what the input state must be for the corresponding

high-speed counter action to occur:

Bidirectional Counter (Encoder)

Input State

H g -Speed

Input A

(I/0)

Input B

(I/1)

HSC Rung

High-Speed

Counter Action

Turning On

Off

True

Count Up

Turning Off

Off

True

Count Down

NA

On

NA

Hold Count

NA

NA

False

Hold Count

Off or On

NA

NA

Hold Count

NA (Not Applicable)

Bidirectional Counter with Reset and Hold (Encoder)

Input State

H g -Speed

Input A

(I/0)

Input B

(I/1)

Input Z

(I/2)

Input Hold

(I/3)

HSC Rung

High-Speed

Counter Action

Turning On

Off

Off

Off

True

Count Up

Turning Off

Off

Off

Off

True

Count Down

Off or On

NA

Off

NA

NA

Hold Count

NA

On

Off

NA

NA

Hold Count

NA

NA

Off

NA

False

Hold Count

NA

NA

Off

On

NA

Hold Count

Off

Off

On

➀

NA

NA

Reset to 0

NA (Not Applicable)

➀

The optional hardware high-speed counter reset is the logical coincidence of A x B x Z.

Programming

- 20P PowerFlex DC Drive - Frame D Bimetal Thermostat (10 pages)

- 1336S_F_T_E_R F Frame Snubber Resistor Repl. (6 pages)

- 22-COMM PowerFlex 4-Class DSI (Drive Serial Interface) Network Communication Adapter (4 pages)

- 8-545 Plug In Solid State Relay (2 pages)

- 20-HIM-B1 PowerFlex 7-Class HIM Bezel (DPI) (4 pages)

- 100 Contactors with DC Coil (1 page)

- 100 Contactors with DC Coil (2 pages)

- 20P PowerFlex DC Drive - Frame D Switching Power Supply Circuit Board (6 pages)

- 140G-MTFx_MTHx_MTIx_MTKx Trip Unit Installation-140G-M (6 pages)

- 45BRD Analog Laser Sensor (4 pages)

- 20D Multi-Device Interface Option Board for PowerFlex 700S Drives (20 pages)

- 56RF RFID 18 mm Cylindrical Transceiver (2 pages)

- 42KC Miniature Rectangular: 5V DC Version (2 pages)

- 20P PowerFlex DC Drive - Frame A Switching Power Supply Circuit Board (16 pages)

- 21P-MISC-A-TP-2 Transition Tube Kit #C19-6/7 For PowerFlex 755 w/OEM Liquid Cooling Fr 6/7 Drive (2 pages)

- 42BT Background Suppression Sensor (3 pages)

- 42CB High Speed 18mm Cylindrical (4 pages)

- 140EX-JE2_JE3 Molded Case Circuit Breaker (4 pages)

- 140G-K-EAM1A Early Make Aux Contact for Rotary Handle Oper Mech-140G-K (1 page)

- 140G-K-EAM1A Early Make Aux Contact for Rotary Handle Oper Mech-140G-K (3 pages)

- 20-HIM-A6 PowerFlex (Human Interface Module) (74 pages)

- 42CF General Purpose 12mm Cylindrical (4 pages)

- 20D PowerFlex 700S Phase II Drive Frames 1...6 (80 pages)

- 140EX-HE1_HE2 Molded Case Circuit Breaker (6 pages)

- 140EX-HE1_HE2 Molded Case Circuit Breaker (4 pages)

- 20B PowerFlex 700 Custom Firmware - Pump Off (12 pages)

- 20-WIM-N4S DPI Wireless Interface Module (92 pages)

- 140U H-Frame Circuit Breaker Fixed and Adjustable Thermal Trip (7 pages)

- 140U H-Frame Circuit Breaker Fixed and Adjustable Thermal Trip (2 pages)

- 60-2619, 42JS Swivel/Tilt Mounting Bracket (1 page)

- 22A PowerFlex 4/40/400 Flange Mount (4 pages)

- 45MLA Controller Installation Instructions (16 pages)

- 20P PowerFlex DC Drive - Cooling Fan for Frame A Drives Above 73A at 230V 460V AC (6 pages)

- 42JS Series 7000 to 42JS VisiSight Replacement Kit (2 pages)

- 22A PowerFlex 4-Class HIM Bezel (DSI) (4 pages)

- 42CS Stainless Steel Photoelectric Sensors (4 pages)

- 20L-LL PowerFlex 700L Liquid-to-Liquid Heat Exchanger (40 pages)

- 20P PowerFlex DC Drive - Frame B SCR Modules (20 pages)

- 22B PowerFlex 40 Quick Start FRN 5.xx - 6.xx (161 pages)

- 22B PowerFlex 40 Quick Start FRN 5.xx - 6.xx (22 pages)

- 22F PowerFlex 4M Input RFI Filters (2 pages)

- 45LFM Capacitive Label Sensor (4 pages)

- 140G-Rx Installation Instruction-140G-R (2 pages)

- 140G-Rx Installation Instruction-140G-R (29 pages)

- 22C PowerFlex 400 AC Drive Quick Start - FRN 1-4.xx (28 pages)