3 clkpr – clock prescaler register, Table 9-10 – Rainbow Electronics ATmega64M1 User Manual

Page 36

36

8209A–AVR–08/09

ATmega16M1/32M1/64M1

When the PLLE is set, the PLL is started and if not yet started the internal RC Oscillator is

started as PLL reference clock. If PLL is selected as a system clock source the value for this bit

is always 1.

• Bit 0 – PLOCK: PLL Lock Detector

When the PLOCK bit is set, the PLL is locked to the reference clock, and it is safe to enable

CLK

PLL

for Fast Peripherals. After the PLL is enabled, it takes about 100 ms for the PLL to lock.

9.11.3

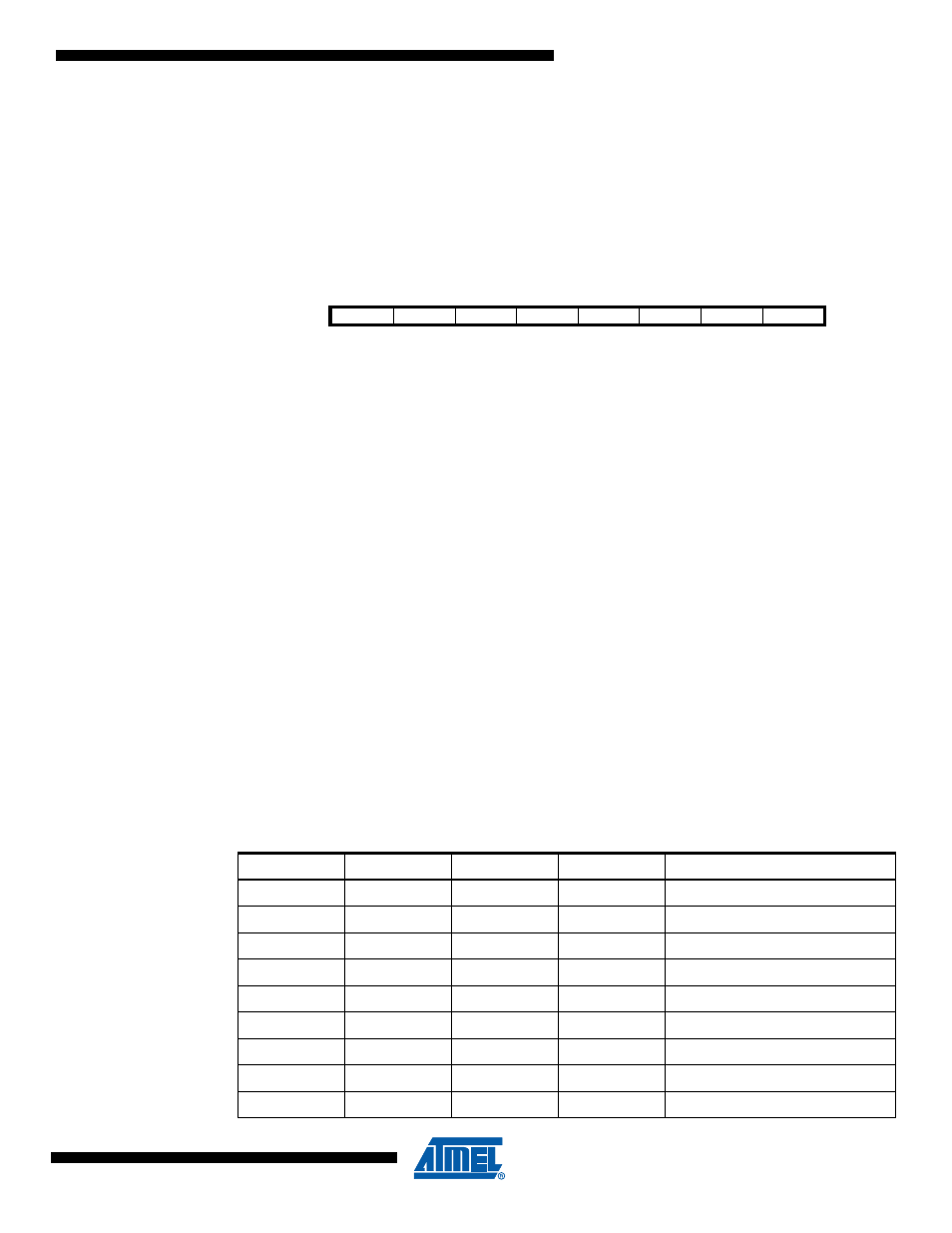

CLKPR – Clock Prescaler Register

• Bit 7 – CLKPCE: Clock Prescaler Change Enable

The CLKPCE bit must be written to logic one to enable change of the CLKPS bits. The CLKPCE

bit is only updated when the other bits in CLKPR are simultaniosly written to zero. CLKPCE is

cleared by hardware four cycles after it is written or when CLKPS bits are written. Rewriting the

CLKPCE bit within this time-out period does neither extend the time-out period, nor clear the

CLKPCE bit.

• Bits 3..0 – CLKPS3..0: Clock Prescaler Select Bits 3 - 0

These bits define the division factor between the selected clock source and the internal system

clock. These bits can be written run-time to vary the clock frequency to suit the application

requirements. As the divider divides the master clock input to the MCU, the speed of all synchro-

nous peripherals is reduced when a division factor is used. The division factors are given in

The CKDIV8 Fuse determines the initial value of the CLKPS bits. If CKDIV8 is unprogrammed,

the CLKPS bits will be reset to “0000”. If CKDIV8 is programmed, CLKPS bits are reset to

“0011”, giving a division factor of 8 at start up. This feature should be used if the selected clock

source has a higher frequency than the maximum frequency of the device at the present operat-

ing conditions. Note that any value can be written to the CLKPS bits regardless of the CKDIV8

Fuse setting. The Application software must ensure that a sufficient division factor is chosen if

the selcted clock source has a higher frequency than the maximum frequency of the device at

the present operating conditions. The device is shipped with the CKDIV8 Fuse programmed.

Bit

7

6

5

4

3

2

1

0

CLKPCE

–

–

–

CLKPS3

CLKPS2

CLKPS1

CLKPS0

CLKPR

Read/Write

R/W

R

R

R

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

See Bit Description

Table 9-10.

Clock Prescaler Select

CLKPS3

CLKPS2

CLKPS1

CLKPS0

Clock Division Factor

0

0

0

0

1

0

0

0

1

2

0

0

1

0

4

0

0

1

1

8

0

1

0

0

16

0

1

0

1

32

0

1

1

0

64

0

1

1

1

128

1

0

0

0

256