15 interrupts, 1 interrupt vector, 2 psc interrupt vectors in atmega16m1/32m1/64m1 – Rainbow Electronics ATmega64M1 User Manual

Page 147: 16 register description, 1 poc – psc output configuration

147

8209A–AVR–08/09

ATmega16M1/32M1/64M1

18.15 Interrupts

T h i s s e c t i o n d e s c r i b e s t h e s p e c i f i c s o f t h e i n t e r r u p t h a n d l i n g a s p e r f o r m e d i n

ATmega16M1/32M1/64M1.

18.15.1

Interrupt Vector

PSC provides 2 interrupt vectors:

• PSC_End (End of Cycle): When enabled and when a match with POCR_RB occurs

• PSC_Fault (Fault Event): When enabled and when a PSC input detects a Fault event.

18.15.2

PSC Interrupt Vectors in ATmega16M1/32M1/64M1

18.16 Register Description

Registers are explained for PSC module 0. They are identical for module 1 and module 2.

18.16.1

POC – PSC Output Configuration

• Bit 7:6 – Res: Reserved

These bits are reserved and will always read as zero.

• Bit 5 – POEN2B: PSC Output 2B Enable

When this bit is clear, I/O pin affected to PSCOUT2B acts as a standard port.

0

1

1

CLK I/O / 256

1

0

0

CLK PLL

1

0

1

CLK PLL / 4

1

1

0

CLK PLL / 32

1

1

1

CLK PLL / 256

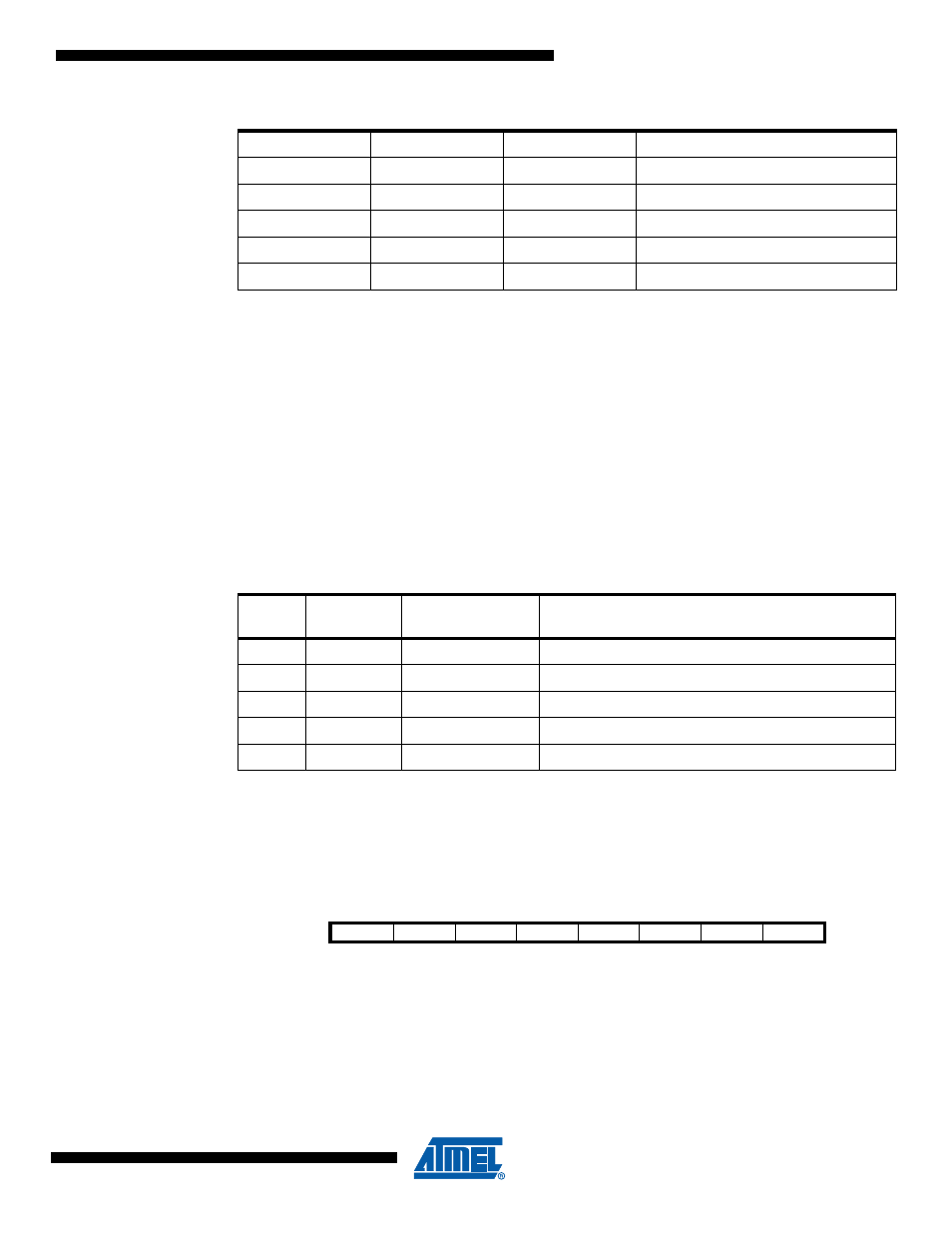

Table 18-6.

Output Clock versus Selection and Prescaler

PCLKSELn

PPREn1

PPREn0

CLKPSCn output

Table 18-7.

PSC Interrupt Vectors

Vector

No.

Program

Address

Source

Interrupt Definition

-

-

-

-

5

0x0004

PSC_Fault

PSC Fault event

6

0x0005

PSC_End

PSC End of Cycle

-

-

-

-

-

-

-

-

Bit

7

6

5

4

3

2

1

0

-

-

POEN2B

POEN2A

POEN1B

POEN1A

POEN0B

POEN0A

POC

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0