8 pctl – psc control register, 9 pmicn – psc module n input control register, See “pmicn – psc module n input control – Rainbow Electronics ATmega64M1 User Manual

Page 151

151

8209A–AVR–08/09

ATmega16M1/32M1/64M1

• Bit 1:0 – Res: Reserved

These bits are reserved and will always read as zero.

18.16.8

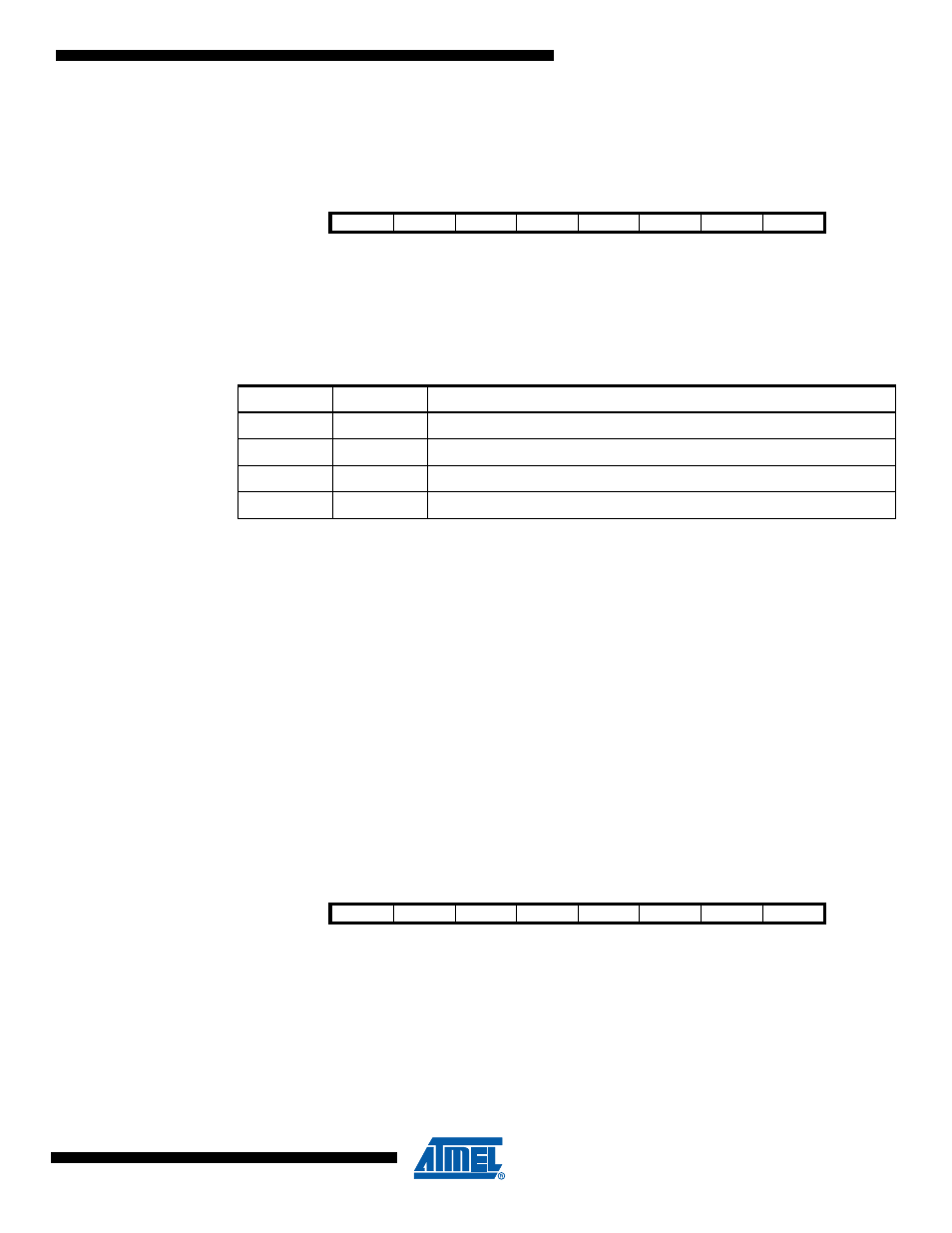

PCTL – PSC Control Register

• Bit 7:6 – PPRE1:0 : PSC Prescaler Select

This two bits select the PSC input clock division factor. All generated waveform will be modified

by this factor.

• Bit 5 – PCLKSEL: PSC Input Clock Select

This bit is used to select between CLK

PLL

or CLK

IO

clocks.

Set this bit to select the fast clock input (CLK

PLL

).

Clear this bit to select the slow clock input (CLK

IO

).

• Bit 4:2 – Res: Reserved

These bits are reserved and will always read as zero.

• Bit 1 – PCCYC: PSC Complete Cycle

When this bit is set, the PSC completes the entire waveform cycle before halt operation

requested by clearing PRUN.

• Bit 0 – PRUN: PSC Run

Writing this bit to one starts the PSC.

18.16.9

PMICn – PSC Module n Input Control Register

The Input Control Registers are used to configure the 2 PSC’s Retrigger/Fault block A & B. The

2 blocks are identical, so they are configured on the same way.

• Bit 7 – POVENn: PSC Module n Overlap Enable

Set this bit to disactivate the Overlap Protection. See

“Overlap Protection” on page 141

Bit

7

6

5

4

3

2

1

0

PPRE1

PPRE0

PCLKSEL

-

-

-

PCCYC

PRUN

PCTL

Read/Write

R/W

R/W

R/W

R

R

R

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0

Table 18-11. PSC Prescaler Selection

PPRE1

PPRE0

Description

0

0

No divider on PSC input clock

0

1

Divide the PSC input clock by 4

1

0

Divide the PSC input clock by 32

1

1

Divide the PSC clock by 256

Bit

7

6

5

4

3

2

1

0

POVENn

PISELn

PELEVn

PFLTEn

PAOCn

PRFMn2

PRFMn1

PRFMn0

PMICn

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0