1 cangcon – can general control register – Rainbow Electronics ATmega64M1 User Manual

Page 183

183

8209A–AVR–08/09

ATmega16M1/32M1/64M1

20.10.1

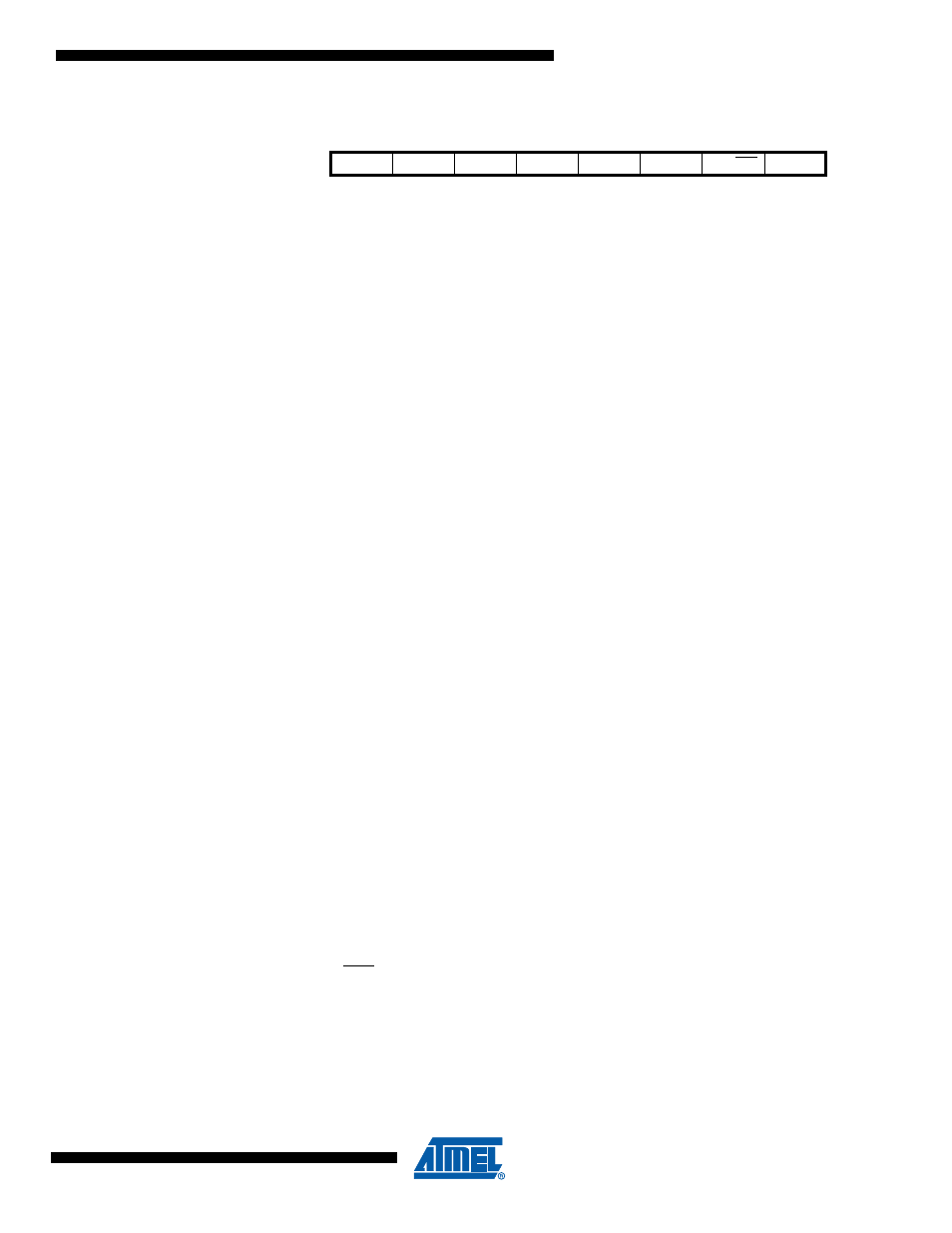

CANGCON – CAN General Control Register

• Bit 7 – ABRQ: Abort Request

This is not an auto resettable bit.

– 0 - no request.

– 1 - abort request: a reset of CANEN1 and CANEN2 registers is done. The pending

communications are immediately disabled and the on-going one will be normally

terminated, setting the appropriate status flags.

Note that CANCDMOB register remain unchanged.

• Bit 6 – OVRQ: Overload Frame Request

This is not an auto resettable bit.

– 0 - no request.

– 1 - overload frame request: send an overload frame after the next received frame.

The overload frame can be traced observing OVFG in CANGSTA register (c.f.

).

• Bit 5 – TTC: Time Trigger Communication

– 0 - no TTC.

– 1 - TTC mode.

• Bit 4 – SYNTTC: Synchronization of TTC

This bit is only used in TTC mode.

– 0 - the TTC timer is caught on SOF.

– 1 - the TTC timer is caught on the last bit of the EOF.

• Bit 3 – LISTEN: Listening Mode

– 0 - no listening mode.

– 1 - listening mode.

• Bit 2 – TEST: Test Mode

– 0 - no test mode

– 1 - test mode: intend for factory testing and not for customer use.

Note:

CAN may malfunction if this bit is set.

• Bit 1 – ENA/STB: Enable / Standby Mode

Because this bit is a command and is not immediately effective, the ENFG bit in CANGSTA reg-

ister gives the true state of the chosen mode.

Bit

7

6

5

4

3

2

1

0

ABRQ

OVRQ

TTC

SYNTTC

LISTEN

TEST

ENA/STB

SWRES

CANGCON

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0