12 analog synchronization, 13 interrupt handling, 14 psc clock sources – Rainbow Electronics ATmega64M1 User Manual

Page 146

146

8209A–AVR–08/09

ATmega16M1/32M1/64M1

18.12 Analog Synchronization

Each PSC module generates a signal to synchronize the ADC sample and hold; synchronisation

is mandatory for measurements.

This signal can be selected between all falling or rising edge of PSCOUTnA or PSCOUTnB

outputs.

In center aligned mode, OCRnRAH/L is not used, so it can be used to specified the synchroniza-

tion of the ADC. It this case, it’s minimum value is 1.

18.13 Interrupt Handling

As each PSC module can be dedicated for one function, each PSC has its own interrupt system.

List of interrupt sources:

• Counter reload (end of On Time 1)

• PSC Input event (active edge or at the beginning of level configured event)

• PSC Mutual Synchronization Error

18.14 PSC Clock Sources

Each PSC has two clock inputs:

• CLK PLL from the PLL

• CLK I/O

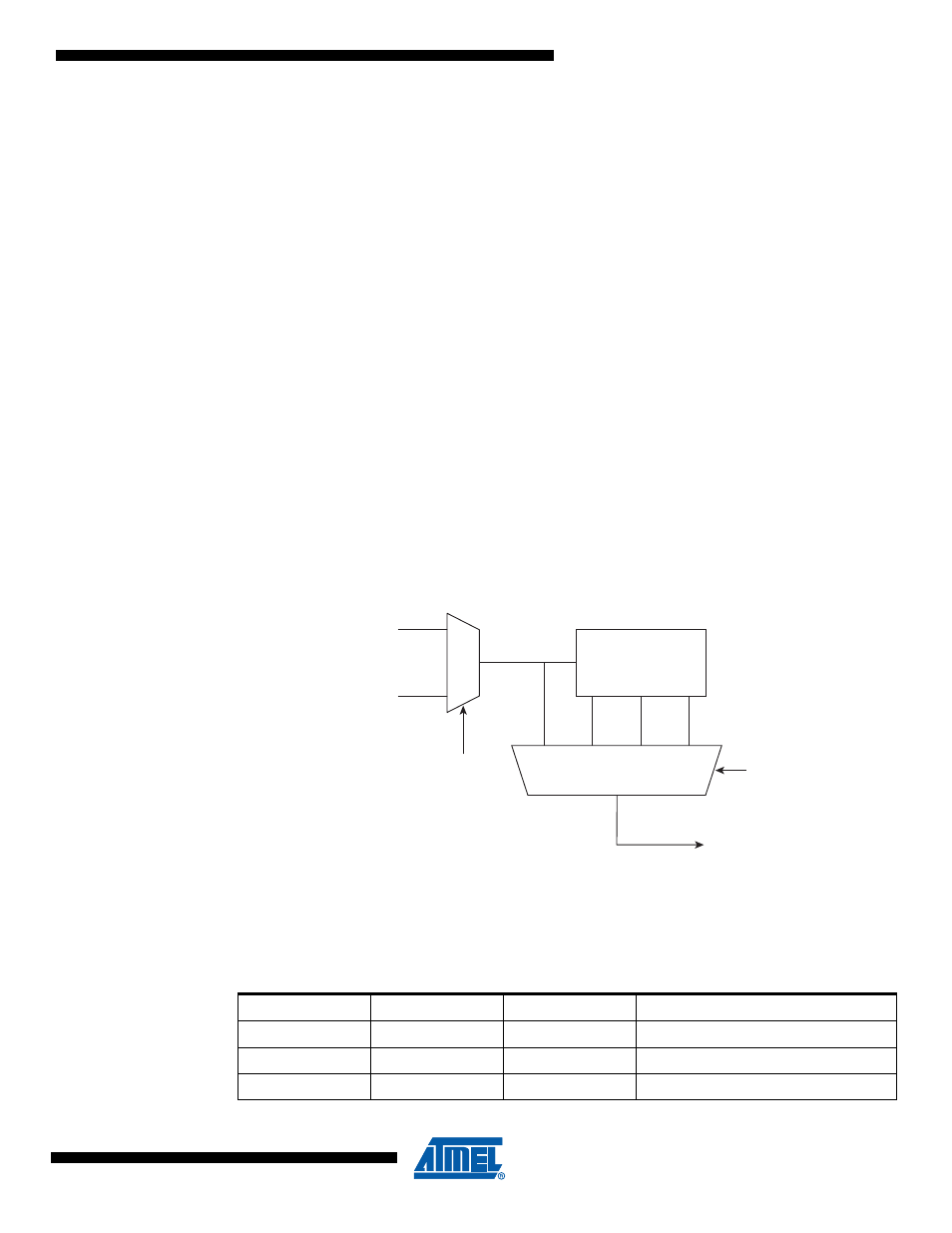

Figure 18-15. Clock selection

PCLKSELn bit in PSC Control Register (PCTL) is used to select the clock source.

PPREn1/0 bits in PSC Control Register (PCTL) are used to select the divide factor of the clock.

Table 18-6.

Output Clock versus Selection and Prescaler

PCLKSELn

PPREn1

PPREn0

CLKPSCn output

0

0

0

CLK I/O

0

0

1

CLK I/O / 4

0

1

0

CLK I/O / 32

CLK

CLK

PSCn

CLK

PLL

I/O

CK

CK/4

CK/32

CK/256

PRESCALER

CK

PPREn1/0

00

01

10

11

PCLKSEL

1

0