5 linbtr – lin bit timing register, 6 linbrr – lin baud rate register, 7 lindlr – lin data length register – Rainbow Electronics ATmega64M1 User Manual

Page 222

222

8209A–AVR–08/09

ATmega16M1/32M1/64M1

This bit is cleared when LERR bit in LINSIR is cleared.

• Bit 0 - LBERR: Bit Error Flag

– 0 = no error,

– 1 = Bit error.

This bit is cleared when LERR bit in LINSIR is cleared.

21.6.5

LINBTR – LIN Bit Timing Register

• Bit 7 - LDISR: Disable Bit Timing Re synchronization

– 0 = Bit timing re-synchronization enabled (default),

– 1 = Bit timing re-synchronization disabled.

• Bits 5:0 - LBT[5:0]: LIN Bit Timing

Gives the number of samples of a bit.

sample-time = (1 /

f

clk

i/o

) x (LDIV[11..0] + 1)

Default value: LBT[6:0]=32 — Min. value: LBT[6:0]=8 — Max. value: LBT[6:0]=63

21.6.6

LINBRR – LIN Baud Rate Register

• Bits 15:12 - Reserved Bits

These bits are reserved for future use. For compatibility with future devices, they must be

written to zero when LINBRR is written.

• Bits 11:0 - LDIV[11:0]: Scaling of clk

i/o

Frequency

The LDIV value is used to scale the entering clk

i/o

frequency to achieve appropriate LIN or

UART baud rate.

21.6.7

LINDLR – LIN Data Length Register

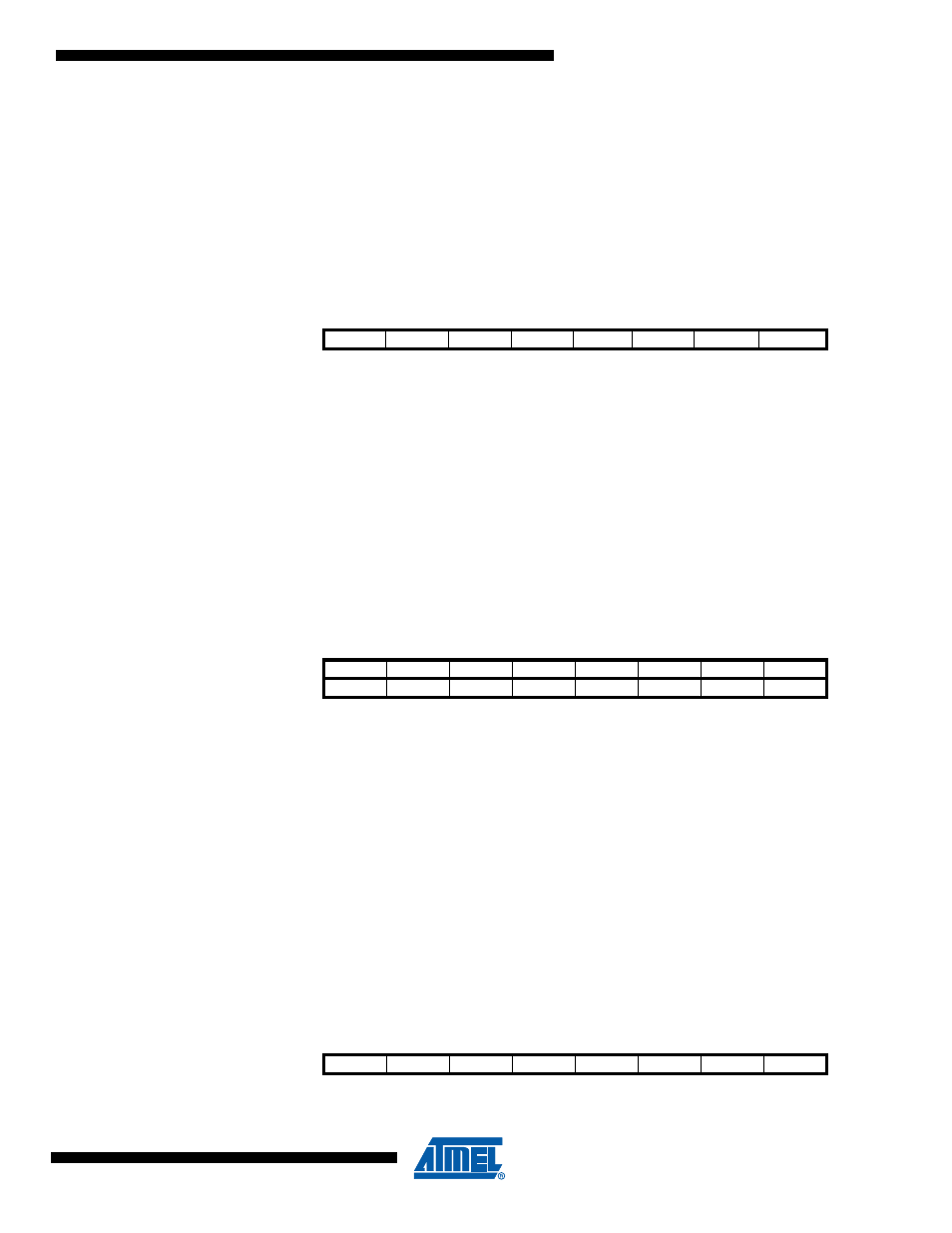

Bit

7

6

5

4

3

2

1

0

LDISR

-

LBT5

LBT4

LBT3

LBT2

LBT1

LBT0

LINBTR

Read/Write

R/W

R

R/(W)

R/(W)

R/(W)

R/(W)

R/(W)

R/(W)

Initial Value

0

0

1

0

0

0

0

0

Bit

7

6

5

4

3

2

1

0

LDIV7

LDIV6

LDIV5

LDIV4

LDIV3

LDIV2

LDIV1

LDIV0

LINBRRL

-

-

-

-

LDIV11

LDIV10

LDIV9

LDIV8

LINBRRH

Bit

15

14

13

12

11

10

9

8

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0

Bit

7

6

5

4

3

2

1

0

LTXDL3

LTXDL2

LTXDL1

LTXDL0

LRXDL3

LRXDL2

LRXDL1

LRXDL0

LINDLR

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0