6 instruction execution timing – Rainbow Electronics ATmega64M1 User Manual

Page 15

15

8209A–AVR–08/09

ATmega16M1/32M1/64M1

7.5.1

SPH and SPL – Stack Pointer High and Stack Pointer Low Register

7.6

Instruction Execution Timing

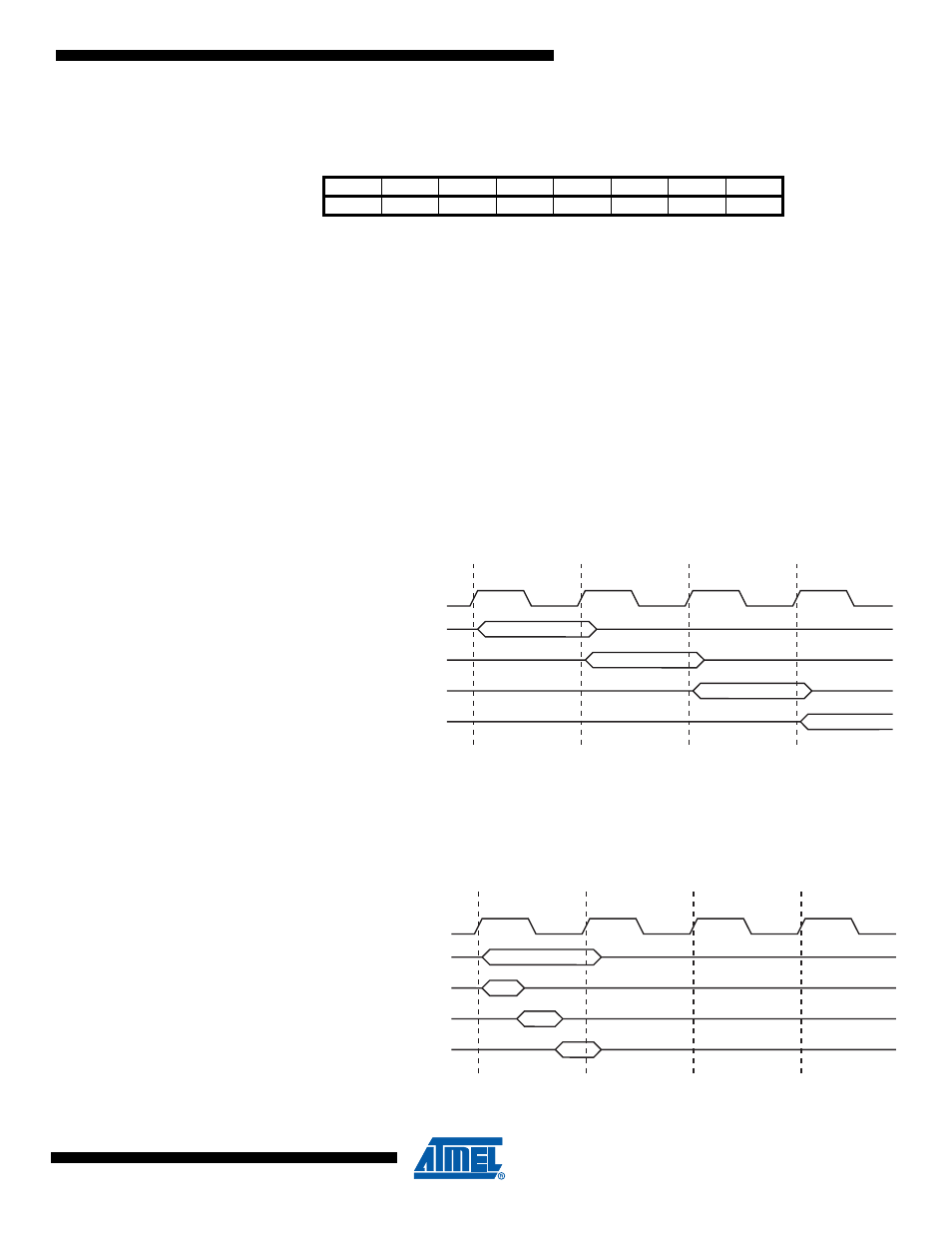

This section describes the general access timing concepts for instruction execution. The AVR

CPU is driven by the CPU clock clk

CPU

, directly generated from the selected clock source for the

chip. No internal clock division is used.

shows the parallel instruction fetches and instruction executions enabled by the Har-

vard architecture and the fast-access Register File concept. This is the basic pipelining concept

to obtain up to 1 MIPS per MHz with the corresponding unique results for functions per cost,

functions per clocks, and functions per power-unit.

Figure 7-4.

The Parallel Instruction Fetches and Instruction Executions

shows the internal timing concept for the Register File. In a single clock cycle an ALU

operation using two register operands is executed, and the result is stored back to the destina-

tion register.

Figure 7-5.

Single Cycle ALU Operation

Bit

15

14

13

12

11

10

9

8

SP15

SP14

SP13

SP12

SP11

SP10

SP9

SP8

SPH

SP7

SP6

SP5

SP4

SP3

SP2

SP1

SP0

SPL

7

6

5

4

3

2

1

0

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

clk

1st Instruction Fetch

1st Instruction Execute

2nd Instruction Fetch

2nd Instruction Execute

3rd Instruction Fetch

3rd Instruction Execute

4th Instruction Fetch

T1

T2

T3

T4

CPU

Total Execution Time

Register Operands Fetch

ALU Operation Execute

Result Write Back

T1

T2

T3

T4

clk

CPU