Comtech EF Data DMD20 User Manual

Page 68

DMD20/DMD50/DMD2050/DMD2050E/DMD1050/OM20 Remote Protocol

Remote Operations

MN-DMDREMOTEOP Revision 9

1–58

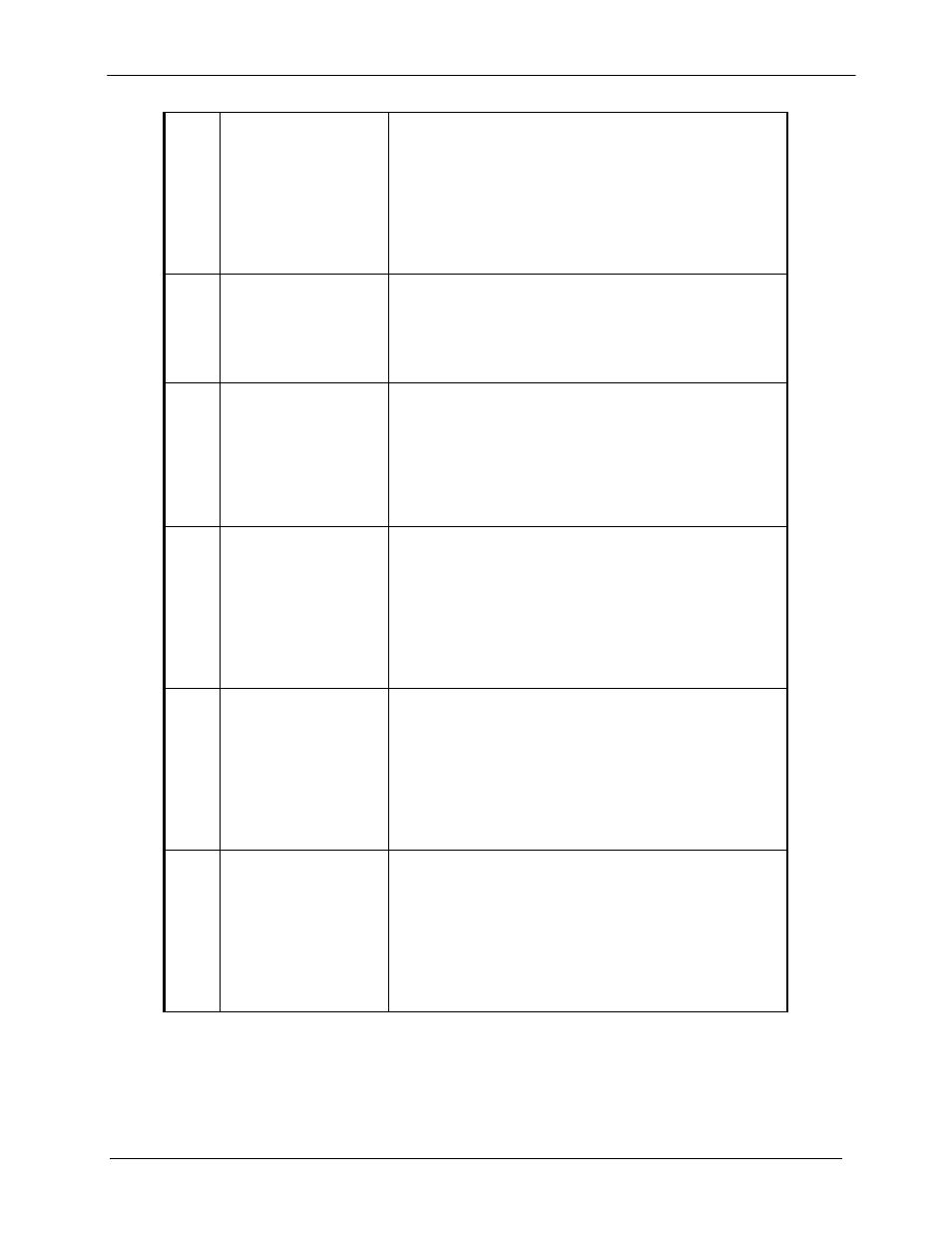

<1>

Alarm 4

Bit 0 = Buffer Clock Activity Detect, 1 = Activity

Bit 1 = External BNC Activity Detect, 1 = Activity

Bit 2 = Rx Satellite Clock Activity Detect, 1 = Activity

Bit 3 = Insert Clock Activity Detect, 1 = Activity

Bit 4 = External Reference Activity Detect, 1 = Activity

Bit 5 = High Stability Reference PLL Activity, 1 =

Activity

Bit 6 = Reserved

Bit 7 = Low EbNo, 1 = Fail

<1>

Common Alarm 1

Bit 0 = -12V Alarm, 1 = Fail

Bit 1 = +12V Alarm, 1 = Fail

Bit 2 = +5V Alarm, 1 = Fail

Bits 3 – 5 = Reserved

Bit 6 = IF SYNTH Alarm, 1 = Fail

Bit 7 = Spare

<1>

Common Alarm 2

Bit 0 = TERR FPGA Config, 1 = Fail

Bit 1 = CODEC FPGA Config, 1 = Fail

Bit 2 = CODEC Device Config, 1 = Fail

Bit 3 = TRANSEC Power Test, 1 = Fail

Bit 4 = +1.5 V Rx Alarm, 1 = Fail

Bit 5 = +1.5 V TX Alarm, 1 = Fail

Bit 6 = +3.3 V Alarm, 1 = Fail

Bit 7 = +20 V Alarm, 1 = Fail

<1>

Latched Alarm 1

Bit 0 = Receive FPGA/Processor Fault

Bit 1 = Carrier Loss

Bit 2 = Multiframe Sync Loss

Bit 3 = Frame Sync Loss

Bit 4 = IBS BER Alarm

Bit 5 = Satellite AIS

Bit 6 = Rx Data Activity

Bit 7 = Rx AGC Level

0 = Not Latched, 1 = Latched

<1>

Latched Alarm 2

Bit 0 = Buffer Underflow

Bit 1 = Buffer Overflow

Bit 2 = Buffer Under 10%

Bit 3 = Buffer Over 90%

Bit 4 = RS Decoder Lock Fault

Bit 5 = RS De-Interleaver Fault

Bit 6 = RS Decoder Uncorrectable Word

Bit 7 = Reserved

0 = Not Latched, 1 = Latched

<1>

Latched Alarm 3

Bit 0 = Rx L-Band Synthesizer Lock

Bit 1 = Insert DSP Config

Bit 2 = Buffer Clock PLL Lock Detect

Bit 3 = Viterbi Decoder Lock

Bit 4 = Sequential Decoder Lock

Bit 5 = Rx Test Pattern Lock

Bit 6 = External Reference PLL Lock

Bit 7 = Rx Carrier Level

0 = Not Latched, 1 = Latched