3 adc control register (adcn, m4[0eh]), Maxq family user’s guide: maxq2010 supplement – Maxim Integrated MAXQ Family Users Guide: MAXQ2010 Supplement User Manual

Page 87

MAXQ Family User’s Guide:

MAXQ2010 Supplement

19-5

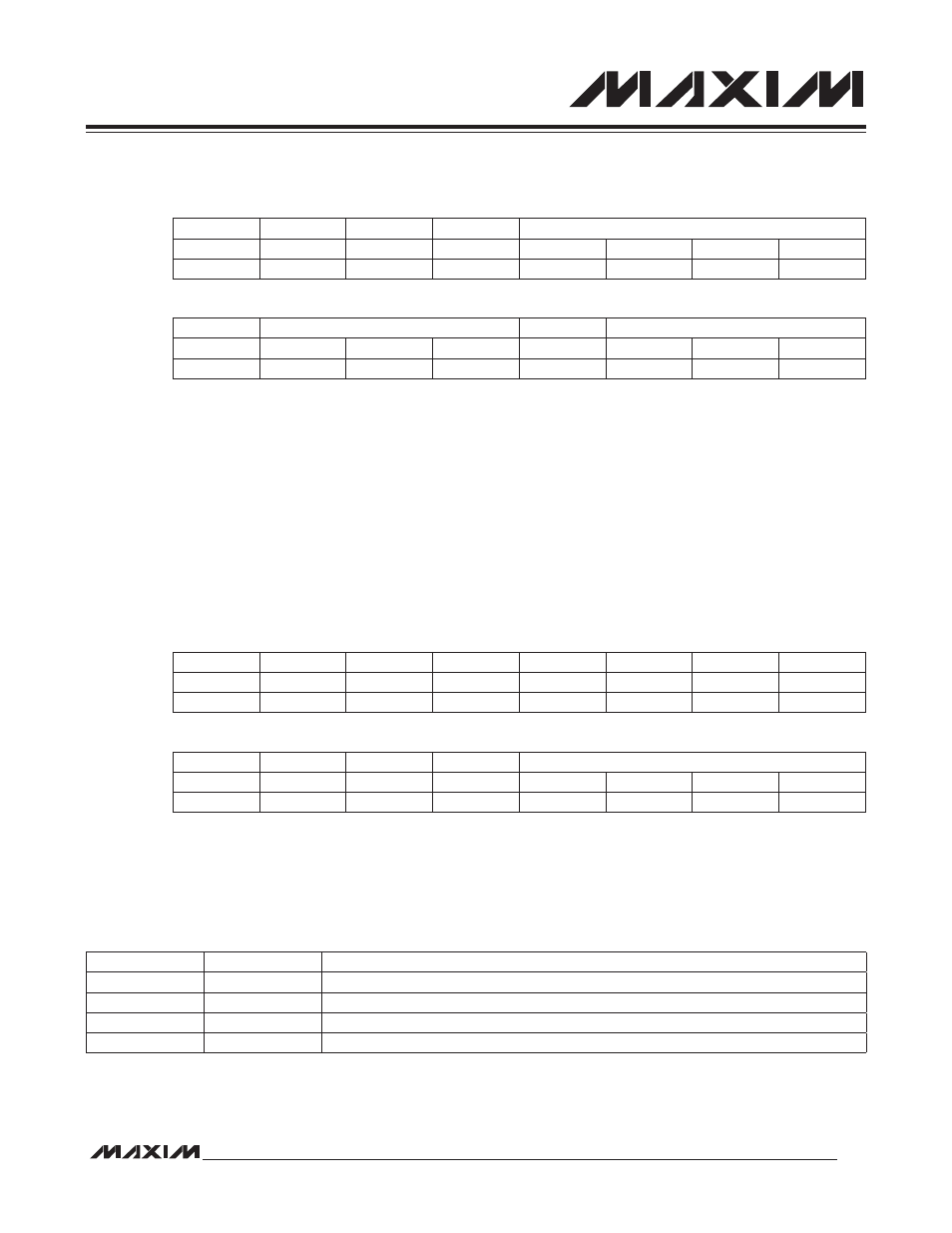

19.2.2 ADC Conversion Sequence Address Register (ADADDR, M4[07h])

Bits 15:12, 7, 3: Reserved

Bits 11:8: ADC Sequence Sample Storage Address (SEQSTORE[3:0]). These bits contain the index of the first

ADBUF register (inclusive) that is used to store samples from the ADC conversion sequence.

Bits 6:4: ADC Sequence Start Address (SEQSTART[2:0]). These bits contain the index of the first ADCFG register

(inclusive) that is used to define the ADC conversion sequence.

Bits 2:0: ADC Sequence End Address (SEQEND[2:0]). These bits contain the index of the last ADCFG register (inclu-

sive) that is used to define the ADC conversion sequence.

19.2.3 ADC Control Register (ADCN, M4[0Eh])

Bits 15:12: Reserved

Bits 11:10: ADC Data Available Interrupt Interval (ADINT[1:0]). These bits select the condition for generating an

ADC data available interrupt (setting ADDAI to 1).

*Can only be written when ADCONV = 0.

*Can only be written when ADCONV = 0.

Bit #

15

14

13

12

11

10

9

8

Name

—

—

—

—

SEQSTORE[3:0]

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

rw*

rw*

rw*

rw*

Bit #

7

6

5

4

3

2

1

0

Name

—

SEQSTART[2:0]

—

SEQEND[2:0]

Reset

0

0

0

0

0

0

0

0

Access

r

rw*

rw*

rw*

r

rw*

rw*

rw*

Bit #

15

14

13

12

11

10

9

8

Name

—

—

—

—

ADINT1

ADINT0

ADCLK1

ADCLK0

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

rw*

rw*

rw*

rw*

Bit #

7

6

5

4

3

2

1

0

Name

IREFEN

ADCONT

ADDAIE

ADPMO

ADACQ[3:0]

Reset

0

0

0

0

0

0

0

0

Access

rw*

rw*

rw*

rw*

rw*

rw*

rw*

rw*

ADINT1

ADINT0

SET ADDAI to 1 . . .

0

0

After each ADC conversion (every sample)

0

1

After the conversion sequence has completed (works for single-conversion mode only)

1

0

Every 12 ADC samples

1

1

Every 16 ADC samples