5 rtc seconds counter low register (rtsl, m0[1ch]), Maxq family user’s guide: maxq2010 supplement – Maxim Integrated MAXQ Family Users Guide: MAXQ2010 Supplement User Manual

Page 68

MAXQ Family User’s Guide:

MAXQ2010 Supplement

14-6

14.4.3 Real-Time Subsecond Counter Register (RTSS, M0[1Ah])

Bits 7:0: RTC Subsecond Counter Register. This ripple counter represents 1/256-second resolution for the RTC and

its content is incremented with each 256Hz clock tick derived from the 32.768kHz oscillator. When the counter rolls

over, its output is used to drive the 32-bit second counter.

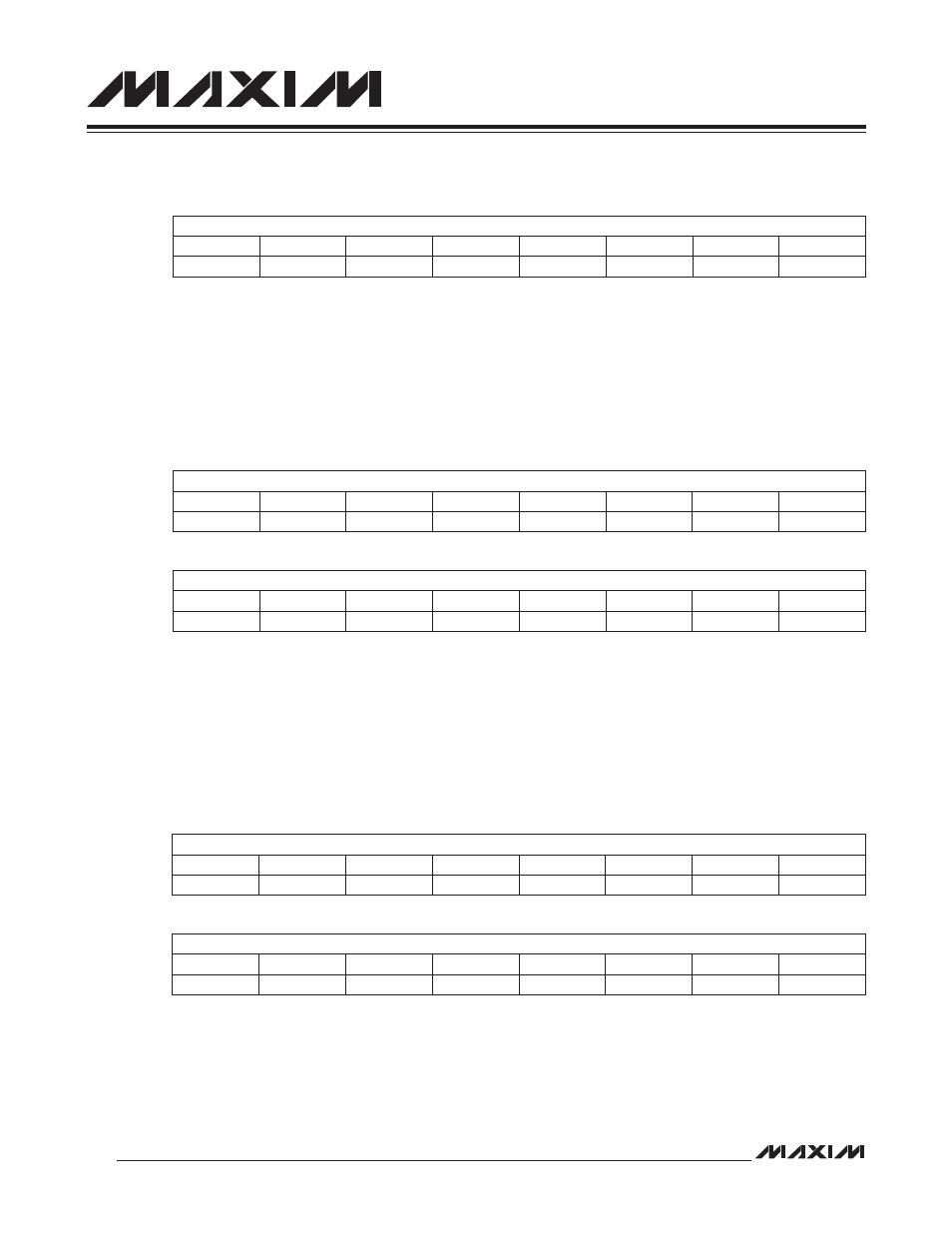

14.4.4 RTC Seconds Counter High Register (RTSH, M0[1Bh])

Bits 15:0: RTC Second Counter High Register. This register contains the most significant bits for the 32-bit second

counter. The RTC is a 48-bit ripple counter consisting of three cascaded counter registers: the 8-bit subsecond counter

(RTSS), the 16-bit low-order seconds counter (RTSL), and the 16-bit high-order second counter (RTSH).

14.4.5 RTC Seconds Counter Low Register (RTSL, M0[1Ch])

Bits 15:0: RTC Second Counter Low Register. This register contains the least significant bits for the 32-bit second

counter. The RTC is a 48-bit ripple counter consisting of three cascaded counter registers: the 8-bit subsecond counter

(RTSS), the 16-bit low-order seconds counter (RTSL), and the 16-bit high-order second counter (RTSH).

Note 1: This register is cleared by power-on reset only.

Note 2: Read accessible when RDY = 1.

Note 3: Write accessible when RTCE = 0 and BUSY = 0.

Note 1: This register is cleared by power-on reset only.

Note 2: Read accessible when RDY = 1.

Note 3: Write accessible when RTCE = 0 and BUSY = 0.

Note 1: This register is cleared by power-on reset only.

Note 2: Read accessible when RDY = 1.

Note 3: Write accessible when RTCE = 0 and BUSY = 0.

Bit #

15

14

13

12

11

10

9

8

Name

RTSH

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

RTSH

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

15

14

13

12

11

10

9

8

Name

RTSL

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

RTSL

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

RTSS

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw