6 rtc subsecond alarm register (rssa, m0[1dh]), Maxq family user’s guide: maxq2010 supplement – Maxim Integrated MAXQ Family Users Guide: MAXQ2010 Supplement User Manual

Page 69

MAXQ Family User’s Guide:

MAXQ2010 Supplement

14-7

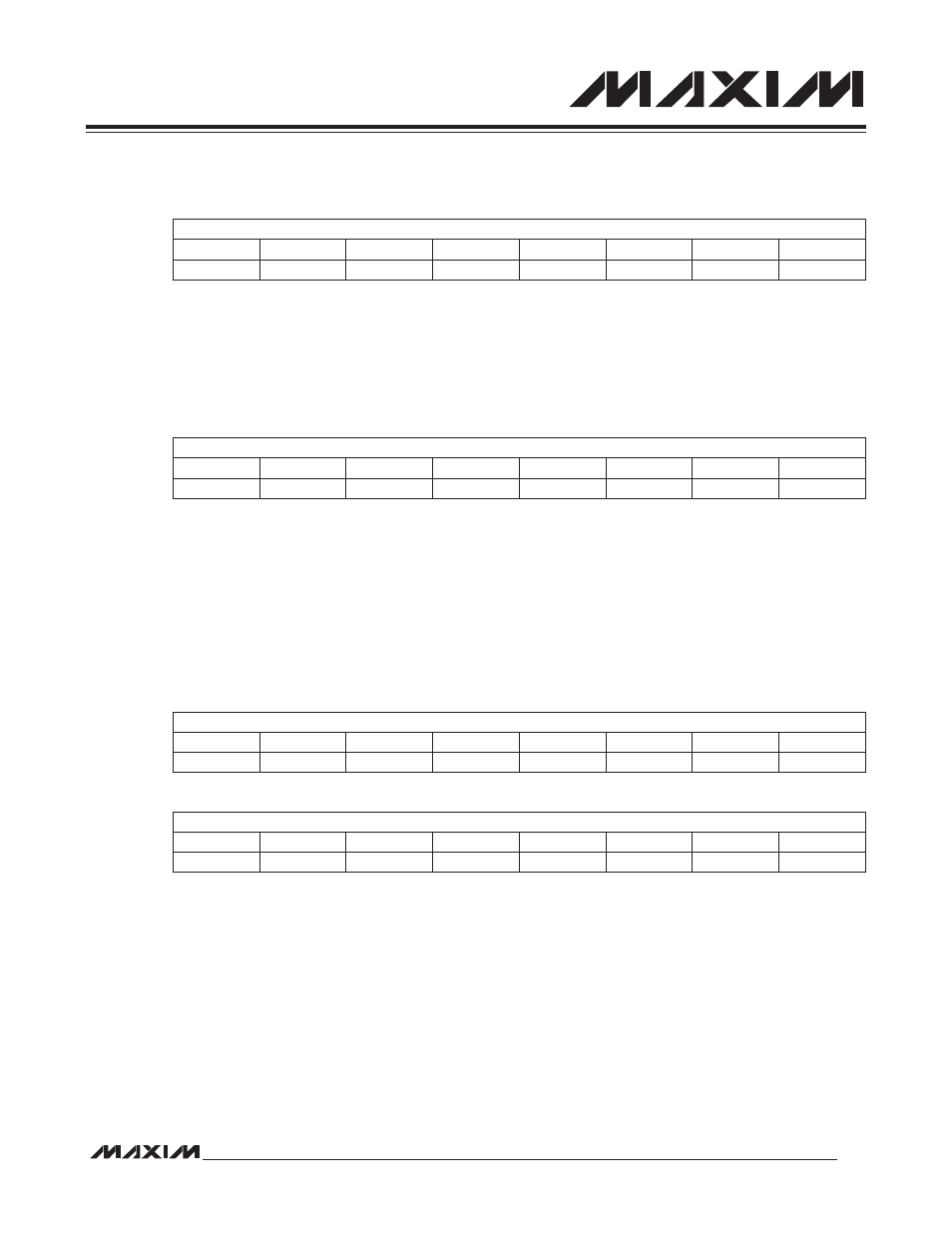

14.4.6 RTC Subsecond Alarm Register (RSSA, M0[1Dh])

Bits 7:0: RTC Subsecond Alarm Register. This register contains the reload value for the subsecond alarm. The ALSF

bit is set when an autoreload occurs.

14.4.7 RTC Time-of-Day Alarm High Register (RASH, M0[1Eh])

Bits 7:0: RTC Time-of-Day Alarm High Register. This register contains the most significant bits for the 24-bit time-of-

day alarm. The time-of-day alarm is formed by the RASH and the RASL registers, and only the lower 20 bits is meaning-

ful for the alarm function. Each time the subsecond counter rolls over (once per second), the RTC compares the lowest

20 bits of the time-of-day alarm setting (RASH[3:0]:RASL[15:0]) with the 20 least significant bits of the seconds counter

(RTSH[3:0]:RTSL[15:0]). The time-of-day alarm is triggered when these two 20-bit values match.

14.4.8 RTC Time-of-Day Alarm Low Register (RASL, M0[1Fh])

Bits 15:0: RTC Time-of-Day Alarm Low Register. This register contains the least significant bits for the 20-bit time-of-

day alarm. The time-of-day alarm is formed by the RASH and the RASL registers and only the lower 20 bits are mean-

ingful for the alarm function. Each time the subsecond counter rolls over (once per second), the RTC compares the

lowest 20 bits of the time-of-day alarm setting (RASH[3:0]:RASL[15:0]) with the 20 least significant bits of the seconds

counter (RTSH[3:0]:RTSL[15:0]). The time-of-day alarm is triggered when these two 20-bit values match.

Note: Write accessible when BUSY = 0 and either ASE = 0 or RTCE = 0.

Note: Write accessible when BUSY = 0 and either ASE = 0 or RTCE = 0.

Note: Write accessible when BUSY = 0 and either ASE = 0 or RTCE = 0.

Bit #

7

6

5

4

3

2

1

0

Name

RSSA

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

RASH

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

Rw

Bit #

15

14

13

12

11

10

9

8

Name

RASL

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

RASL

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw