5 system clock control register (ckcn, m8[0eh]), 5 system clock control register (ckcn, m8[0eh]) -5, Maxq family user’s guide: maxq2010 supplement – Maxim Integrated MAXQ Family Users Guide: MAXQ2010 Supplement User Manual

Page 31

MAXQ Family User’s Guide:

MAXQ2010 Supplement

4-5

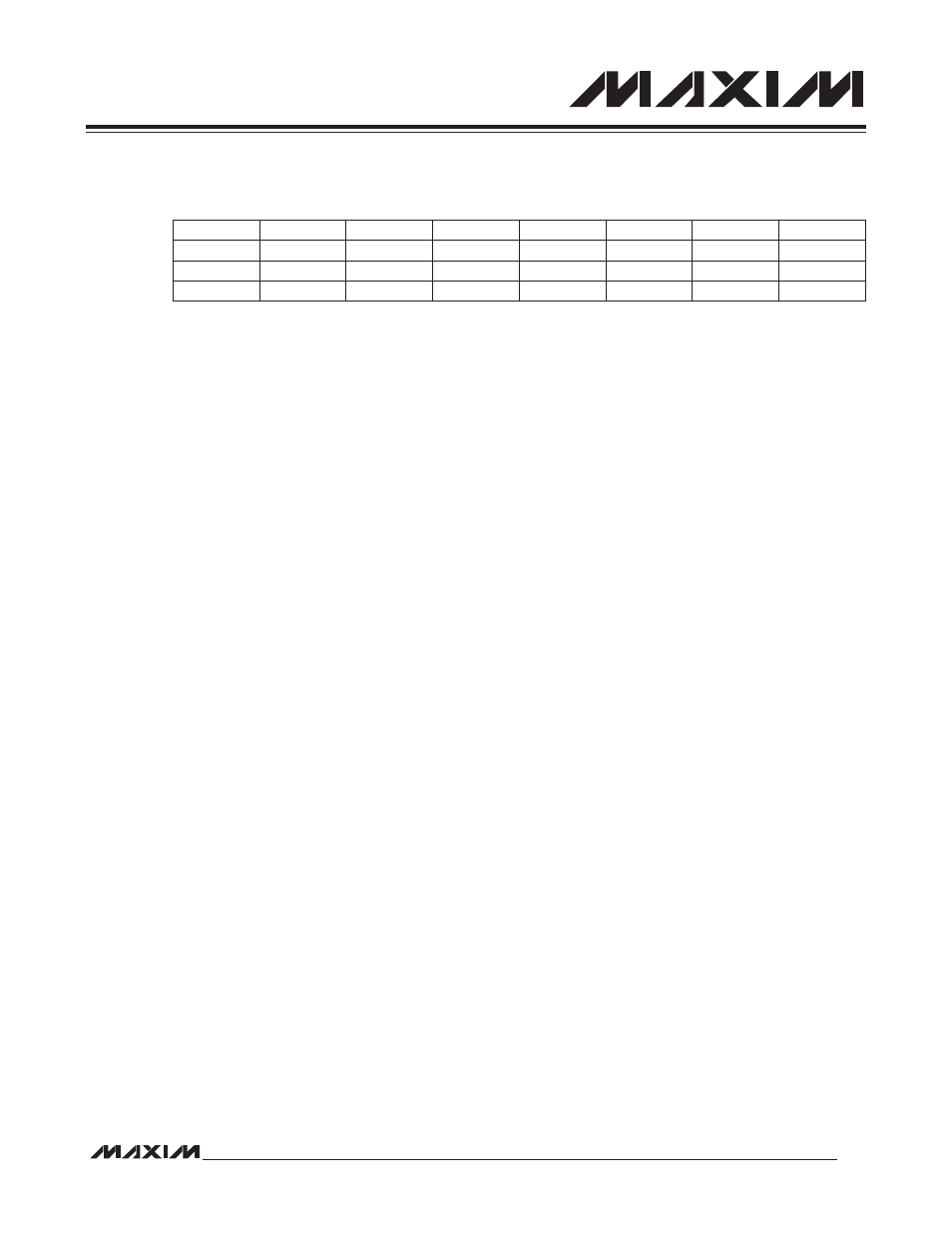

4.1.5 System Clock Control Register (CKCN, M8[0Eh])

The CKCN register bit settings determine the system clock source and clock divider as described in Table 4-4.

Bit 7: Reserved

Bit 6: Frequency-Locked Loop Select (FLLSL)

0 = Selects the high-frequency oscillator as the system clock source.

1 = Selects the FLL as the system clock source.

Bit 5: Frequency-Locked Loop Mode (FLLMD). This read-only status bit indicates the clock source that is currently

being used.

0 = High-frequency oscillator is currently being used as the system clock source, because the FLL is not selected

(FLLSL = 0).

1 = FLL is currently being used as the system clock source. This is either because it is selected as the clock source

(FLLSL = 1), or because the high-frequency oscillator is in the process of warming up.

Bit 4: Stop-Mode Select (STOP). Setting this bit to 1 causes the processor to enter stop mode. This does not change

the currently selected clock-divide ratio.

Bit 3: Switchback Enable (SWB). Setting this bit to 1 enables switchback mode. If power-management mode (divide

by 256) is active and switchback is enabled, the PMME bit is cleared to 0 when any of the following conditions occurs.

• An external interrupt is generated based on an edge detect.

• Either serial port 0 or serial port 1 is enabled to receive data and detects a low condition on its data receive pin.

• Either serial port 0 or serial port 1 has a byte written to its buffer register by software.

• The SPI interface is enabled in master mode, and the SPIB register is written by software.

• The SPI interface is enabled is slave mode, and an external master drives the SSEL line low.

• A START condition occurs on the I

2

C bus, causing an I

2

C start interrupt to be generated.

• The power supply drops below the SVM threshold, causing an SVM interrupt to be generated.

• An ADC conversion is initiated by software by setting the ADCONV bit to 1.

• A time-of-day interrupt or subsecond alarm interrupt occurs from the RTC.

• Debug mode is entered through command entry or a breakpoint match (exits from PMM1 only).

Triggering a switchback condition only clears the PMME bit; the settings of CD0 and CD1 remain the same. When either

power-management mode is active, the SWB bit cannot be set to 1 as long as any of the above conditions are true.

Bit 2: Power-Management Mode Enable (PMME)

Bits 1:0: Clock Divide 1:0 (CD[1:0]). These three bits control the divide ratio or enable power-management mode for

the system clock as shown in Table 4-4. CD0 and CD1 can always be read, and they can be written as long as PMME

= 0.

Setting the PMME bit to 1 activates PMM mode, causing the system clock to be divided by 256. While PMME is set

to 1, CD0 and CD1 cannot be changed; their values determine the clock-divide ratio that is used when the processor

exits power-management mode.

*Unrestricted read access. This bit can only be modified when PMME = 0.

Bit #

7

6

5

4

3

2

1

0

Name

—

FLLSL

FLLMD

STOP

SWB

PMME

CD1

CD0

Reset

1

Unchanged

0

0

0

0

0

0

POR

1

0

0

0

0

0

0

0

Access

r

rw

s

rw

rw

rw

rw*

rw*