10 port 2 output register (po2, m0[02h]), 11 port 3 output register (po3, m0[03h]), 12 port 4 output register (po4, m1[00h]) – Maxim Integrated MAXQ Family Users Guide: MAXQ2010 Supplement User Manual

Page 45: 13 port 5 output register (po5, m1[01h]), Maxq family user’s guide: maxq2010 supplement

MAXQ Family User’s Guide:

MAXQ2010 Supplement

6-7

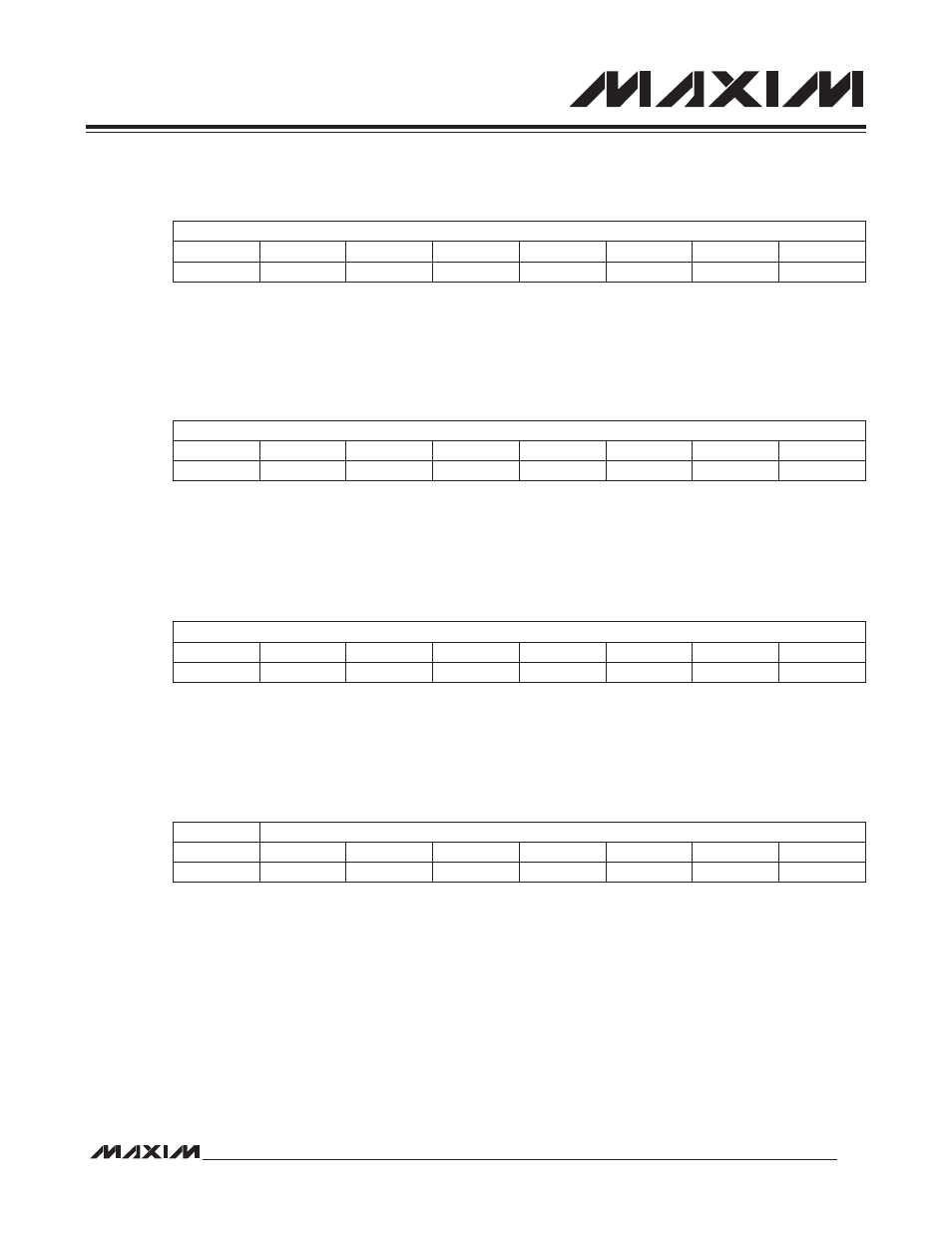

6.1.10 Port 2 Output Register (PO2, M0[02h])

Bits 7:0: Port 2 Output. This register stores the data that is output on any of the pins of port 2 that have been defined

as output pins. If the port pins are in input mode, this register controls the weak pullup for each pin. Changing the data

direction of any pins for this port (through register PD2) does not affect the value in this register.

6.1.11 Port 3 Output Register (PO3, M0[03h])

Bits 7:0: Port 3 Output. This register stores the data that is output on any of the pins of port 3 that have been defined

as output pins. If the port pins are in input mode, this register controls the weak pullup for each pin. Changing the data

direction of any pins for this port (through register PD3) does not affect the value in this register.

6.1.12 Port 4 Output Register (PO4, M1[00h])

Bits 7:0: Port 4 Output. This register stores the data that is output on any of the pins of port 4 that have been defined

as output pins. If the port pins are in input mode, this register controls the weak pullup for each pin. Changing the data

direction of any pins for this port (through register PD4) does not affect the value in this register.

6.1.13 Port 5 Output Register (PO5, M1[01h])

Bits 7:0: Port 5 Output. This register stores the data that is output on any of the pins of port 5 that have been defined

as output pins. If the port pins are in input mode, this register controls the weak pullup for each pin. Changing the data

direction of any pins for this port (through register PD5) does not affect the value in this register.

Bit #

7

6

5

4

3

2

1

0

Name

PO2

Reset

1

1

1

1

1

1

1

1

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

PO3

Reset

1

1

1

1

1

1

1

1

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

PO4

Reset

1

1

1

1

1

1

1

1

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

—

PO5

Reset

1

1

1

1

1

1

1

1

Access

r

rw

rw

rw

rw

rw

rw

rw