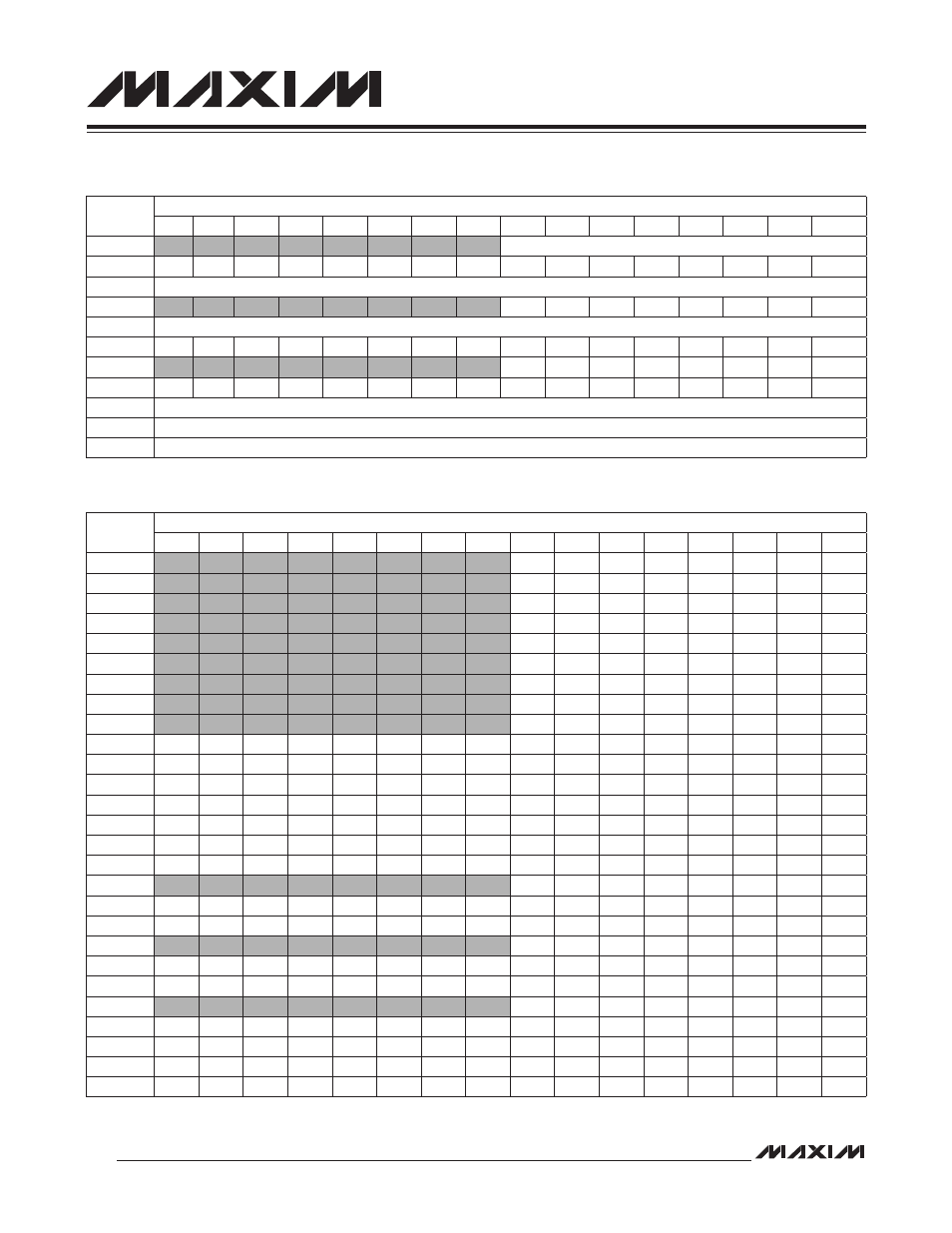

Table 4-3. system register reset values -2, Maxq family user’s guide: maxq2010 supplement – Maxim Integrated MAXQ Family Users Guide: MAXQ2010 Supplement User Manual

Page 28

MAXQ Family User’s Guide:

MAXQ2010 Supplement

4-2

Table 4-2. System Register Bit Functions (continued)

Table 4-3. System Register Reset Values

Note: Bits marked as “s” have special behavior upon reset; see the register descriptions for details.

REG

BIT

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

OFFS

OFFS (8 bits)

DPC

—

—

—

—

—

—

—

—

—

—

—

WBS2 WBS1 WBS0 SDPS1 SDPS0

GR

GR (16 bits)

GRL

GR.7 GR.6 GR.5 GR.4 GR.3 GR.2 GR.1

GR.0

BP

BP (16 bits)

GRS

GR.7 GR.6 GR.5 GR.4 GR.3 GR.2 GR.1 GR.0 GR.15 GR.14 GR.13 GR.12 GR.11 GR.10 GR.9

GR.8

GRH

GR.15 GR.14 GR.13 GR.12 GR.11 GR.10 GR.9

GR.8

GRXL

GR.7 GR.7 GR.7 GR.7 GR.7 GR.7 GR.7 GR.7 GR.7 GR.6 GR.5 GR.4 GR.3 GR.2 GR.1

GR.0

BP[OFFS]

BP[OFFS] (16 bits)

DP[0]

DP[0] (16 bits)

DP[1]

DP[1] (16 bits)

REG

BIT

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

AP

0

0

0

0

0

0

0

0

APC

0

0

0

0

0

0

0

0

PSF

1

0

0

0

0

0

0

0

IC

0

0

0

0

0

0

0

0

IMR

0

0

0

0

0

0

0

0

SC

1

0

0

0

0

0

s

0

IIR

0

0

0

0

0

0

0

0

CKCN

1

s

s

0

0

0

0

0

WDCN

s

s

0

0

0

s

s

0

A[0:15]

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

PFX

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

IP

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

SP

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

IV

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

LC[0]

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

LC[1]

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

OFFS

0

0

0

0

0

0

0

0

DPC

0

0

0

0

0

0

0

0

0

0

0

1

1

1

0

0

GR

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

GRL

0

0

0

0

0

0

0

0

BP

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

GRS

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

GRH

0

0

0

0

0

0

0

0

GRXL

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

BP[OFFS]

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

DP[0]

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

DP[1]

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0