Maxim Integrated MAXQ Family Users Guide: MAXQ2010 Supplement User Manual

Maxq family user’s guide: maxq2010 supplement

_______________________________________________________________ Maxim Integrated Products i

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642,

or visit Maxim’s website at www.maxim-ic.com.

MAXQ FAMILY USER’S GUIDE:

MAXQ2010 SUPPLEMENT

Rev 0; 6/09

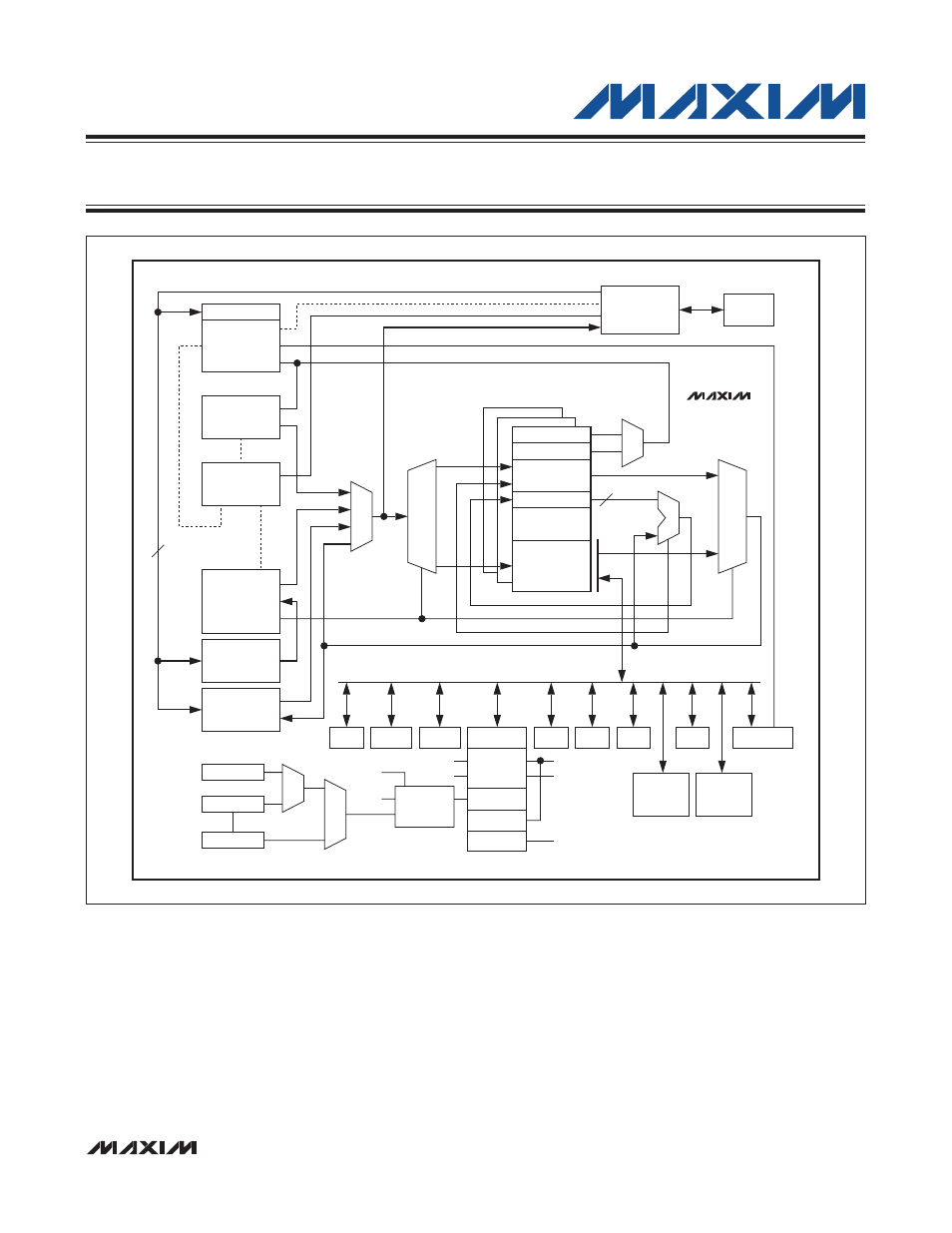

HFX

FLL

32kHz

16

INSTRUCTION

DECODER

PROGRAM

MEMORY

DATA

MEMORY

CONTROL

STACK

ADD REG

ADDRESS

GENERATOR

DEMUX

MUX

IP

DP

SYSTEM

REGISTERS

IN-CIRCUIT

DEBUGGER

PERIPHERAL

REGISTERS

Acc

STATUS

JTAG

INTERRUPT

SUPPLY

VOLTAGE

MONITOR

MAC

WATCHDOG

POWER

OSC UP

BROWNOUT

RESET

LCD

DVDD

DGND

AVDD

AGND

12-BIT

8-CHANNEL

ADC

I

2

C

RTC

SPI

RESET

PMM

STOP

SYSTEM

CLOCK

16

TIMER

USART

MAXQ2010

Table of contents

Document Outline

- ADDENDUM TO SECTION 1: Overview

- ADDENDUM TO SECTION 2: architecture

- ADDENDUM TO SECTION 3: PROGRAMMING

- ADDENDUM TO SECTION 4: SYSTEM REGISTER DESCRIPTIONS

- ADDENDUM TO SECTION 5: PERIPHERAL REGISTER modules

- ADDENDUM TO SECTION 6: GENERAL-PURPOSE I/O MODULE

- 6.1 GPIO and External Interrupt Register Descriptions

- 6.1.1 Port 0 Direction Register (PD0, M0[10h])

- 6.1.2 Port 1 Direction Register (PD1, M0[11h])

- 6.1.3 Port 2 Direction Register (PD2, M0[12h])

- 6.1.4 Port 3 Direction Register (PD3, M0[13h])

- 6.1.5 Port 4 Direction Register (PD4, M1[10h])

- 6.1.6 Port 5 Direction Register (PD5, M1[11h])

- 6.1.7 Port 6 Direction Register (PD6, M1[12h])

- 6.1.8 Port 0 Output Register (PO0, M0[00h])

- 6.1.9 Port 1 Output Register (PO1, M0[01h])

- 6.1.10 Port 2 Output Register (PO2, M0[02h])

- 6.1.11 Port 3 Output Register (PO3, M0[03h])

- 6.1.12 Port 4 Output Register (PO4, M1[00h])

- 6.1.13 Port 5 Output Register (PO5, M1[01h])

- 6.1.14 Port 6 Output Register (PO6, M1[02h])

- 6.1.15 Port 0 Input Register (PI0, M0[08h])

- 6.1.16 Port 1 Input Register (PI1, M0[09h])

- 6.1.17 Port 2 Input Register (PI2, M0[0Ah])

- 6.1.18 Port 3 Input Register (PI3, M0[0Bh])

- 6.1.19 Port 4 Input Register (PI4, M1[08h])

- 6.1.20 Port 5 Input Register (PI5, M1[09h])

- 6.1.21 Port 6 Input Register (PI6, M1[0Ah])

- 6.1.22 External Interrupt Flag 0 Register (EIF0, M0[04h])

- 6.1.23 External Interrupt Flag 1 Register (EIF1, M1[04h])

- 6.1.24 External Interrupt Flag 2 Register (EIF2, M1[06h])

- 6.1.25 External Interrupt Enable 0 Register (EIE0, M0[05h])

- 6.1.26 External Interrupt Enable 1 Register (EIE1, M1[05h])

- 6.1.27 External Interrupt Enable 2 Register (EIE2, M1[07h])

- 6.1.28 External Interrupt Edge Select 0 Register (EIES0, M0[0Ch])

- 6.1.29 External Interrupt Edge Select 1 Register (EIES1, M1[0Bh])

- 6.1.30 External Interrupt Edge Select 2 Register (EIES2, M1[0Ch])

- 6.2 GPIO and External Interrupt Code Examples

- 6.1 GPIO and External Interrupt Register Descriptions

- ADDENDUM TO SECTION 7: TIMER/COUNTER 0 MODULE

- ADDENDUM TO SECTION 8: TIMER/COUNTER 1 MODULE

- ADDENDUM TO SECTION 9: TIMER/COUNTER 2 MODULE

- ADDENDUM TO SECTION 10: SERIAL I/O MODULE

- ADDENDUM TO SECTION 11: SERIAL PERIPHERAL INTERFACE (SPI) MODULE

- ADDENDUM TO SECTION 12: HARDWARE MULTIPLIER MODULE

- ADDENDUM TO SECTION 13: 1-Wire BUS MASTER

- ADDENDUM TO SECTION 14: REAL-TIME CLOCK MODULE

- 14.1 RTC Pins and Control Registers

- 14.2 RTC Operation Overview

- 14.3 RTC Trim Operation

- 14.4 RTC Register Descriptions

- 14.4.1 RTC Trim Register (RTRM, M0[18h])

- 14.4.2 RTC Control Register (RCNT, M0[19h])

- 14.4.3 Real-Time Subsecond Counter Register (RTSS, M0[1Ah])

- 14.4.4 RTC Seconds Counter High Register (RTSH, M0[1Bh])

- 14.4.5 RTC Seconds Counter Low Register (RTSL, M0[1Ch])

- 14.4.6 RTC Subsecond Alarm Register (RSSA, M0[1Dh])

- 14.4.7 RTC Time-of-Day Alarm High Register (RASH, M0[1Eh])

- 14.4.8 RTC Time-of-Day Alarm Low Register (RASL, M0[1Fh])

- 14.5 RTC Example: Starting and Setting the Clock

- ADDENDUM TO SECTION 15: TEST ACCESS PORT (TAP)

- ADDENDUM TO SECTION 16: IN-CIRCUIT DEBUG MODE

- ADDENDUM TO SECTION 17: IN-SYSTEM PROGRAMMING (JTAG)

- 17.1 JTAG Bootloader Protocol

- 17.2 Family 0 Commands (Not Password Protected)

- 17.3 Family 1 Commands: Load Variable Length (Password Protected)

- 17.4 Family 2 Commands: Dump Variable Length (Password Protected)

- 17.5 Family 3 Commands: CRC Variable Length (Password Protected)

- 17.6 Family 4 Commands: Verify Variable Length (Password Protected)

- 17.7 Family 5 Commands: Load and Verify Variable Length (Password Protected)

- 17.8 Family E Commands: Erase Fixed Length (Password Protected)

- ADDENDUM TO SECTION 18: MAXQ FAMILY INSTRUCTION SET SUMMARY

- SECTION 19: ANALOG-TO-DIGITAL CONVERTER (SPECIFIC TO MAXQ2010)

- 19.1 Analog-to-Digital Converter Features

- 19.2 Analog-to-Digital Pins and Control Registers

- 19.2.1 Analog-to-Digital Converter Status Register (ADST, M4[06h])

- 19.2.2 ADC Conversion Sequence Address Register (ADADDR, M4[07h])

- 19.2.3 ADC Control Register (ADCN, M4[0Eh])

- 19.2.4 ADC Data Register (ADDATA, M4[0Fh])

- 19.2.5 ADC Data Buffer Registers (ADBUF[0] to ADBUF[15], ADDATA[00h] to ADDATA[0Fh])

- 19.2.6 ADC Conversion Configuration Registers (ADCFG[0] to ADCFG[7], ADDATA[10h] to ADDATA[17h])

- 19.3 Analog-to-Digital Converter Code Examples

- SECTION 20: LCD CONTROLLER (SPECIFIC TO MAXQ2010)

- 20.1 LCD Controller Overview

- 20.2 LCD Controller Register Descriptions

- 20.2.1 LCD Configuration Register (LCFG, M2[06h])

- 20.2.2 LCD Contrast Adjust Register (LCRA, M2[0Ah])

- 20.2.3 LCD Display Register 0 (LCD0, M2[0Bh])

- 20.2.4 LCD Display Register 1 (LCD1, M2[0Ch])

- 20.2.5 LCD Display Register 2 (LCD2, M2[0Dh])

- 20.2.6 LCD Display Register 3 (LCD3, M2[0Eh])

- 20.2.7 LCD Display Register 4 (LCD4, M2[0Fh])

- 20.2.8 LCD Display Register 5 (LCD5, M2[10h])

- 20.2.9 LCD Display Register 6 (LCD6, M2[11h])

- 20.2.10 LCD Display Register 7 (LCD7, M2[12h])

- 20.2.11 LCD Display Register 8 (LCD8, M2[13h])

- 20.2.12 LCD Display Register 9 (LCD9, M2[14h])

- 20.2.13 LCD Display Register 10 (LCD10, M2[15h])

- 20.2.14 LCD Display Register 11 (LCD11, M2[16h])

- 20.2.15 LCD Display Register 12 (LCD12, M2[17h])

- 20.2.16 LCD Display Register 13 (LCD13, M2[18h])

- 20.2.17 LCD Display Register 14 (LCD14, M2[19h])

- 20.2.18 LCD Display Register 15 (LCD15, M2[1Ah])

- 20.2.19 LCD Display Register 16 (LCD16, M2[1Bh])

- 20.2.20 LCD Display Register 17 (LCD17, M2[1Ch])

- 20.2.21 LCD Display Register 18 (LCD18, M2[1Dh])

- 20.2.22 LCD Display Register 19 (LCD19, M2[1Eh])

- 20.2.23 LCD Display Register 20 (LCD20, M2[1Fh])

- 20.3 LCD Controller Operation Modes

- 20.4 LCD Drive Voltages

- 20.5 Selecting the LCD Display Mode

- 20.6 Segment Pin Configuration

- 20.7 LCD Internal Adjustable Contrast Resistor

- 20.8 LCD Frame Frequency

- 20.9 LCD Display Memory

- 20.10 Display Waveform Generation

- 20.11 LCD Controller Static Drive Example

- 20.12 LCD Controller 1/2 Duty Cycle Drive Example

- 20.13 LCD Controller 1/3 Duty Cycle Drive Example

- 20.14 LCD Controller 1/4 Duty Cycle Drive Example

- 20.15 LCD Controller Example: Initializing the LCD Controller

- SECTION 21: TIMER/COUNTER B MODULE (SPECIFIC TO MAXQ2010)

- 21.1 Timer/Counter B Register Descriptions

- 21.1.1 Timer B Timer/Counter 0/1/2 Capture/Reload Register (TB0R, TB1R, TB2R; M4[00h],M4[02h], M4[04h])

- 21.1.2 Timer B Timer/Counter 0/1/2 Compare Register (TB0C, TB1C, TB2C; M4[01h], M4[03h], M4[05h])

- 21.1.3 Timer B Timer/Counter 0/1/2 Control Register (TB0CN, TB1CN, TB2CN; M4[08h], M4[0Ah], M4[0Ch])

- 21.1.4 Timer B Timer/Counter 0/1/2 Value Register (TB0V, TB1V, TB2V; M4[09h], M4[0Bh], M4[0Dh])

- 21.2 Timer/Counter B Operation

- 21.2.1 Timer B 16-Bit Timer/Counter Mode with Autoreload

- 21.2.2 Timer B 16-Bit Capture Mode

- 21.2.3 Timer B 16-Bit Up/Down Count with Autoreload Mode

- 21.2.4 Timer B Clock Output Mode

- 21.2.5 Timer B PWM/Output Control Functionality

- 21.2.6 16-Bit Up Count PWM/Output Control Mode

- 21.2.7 16-Bit Up/Down Count PWM/Output Control Mode

- 21.2.8 EXENB Control During PWM/Output Control Mode

- 21.3 Timer B Examples

- 21.1 Timer/Counter B Register Descriptions

- SECTION 22 : I2C BUS INTERFACE (SPECIFIC TO MAXQ2010)

- 22.1 I2C Register Descriptions

- 22.1.1 I2C Data Buffer Register (I2CBUF, M3[00h])

- 22.1.2 I2C Status Register (I2CST, M3[01h])

- 22.1.3 Interrupt Enable Register (I2CIE, M3[02h])

- 22.1.4 I2C Control Register (I2CCN, M3[0Ch])

- 22.1.5 Clock Control Register (I2CCK, M3[0Dh])

- 22.1.6 I2C Timeout Register (I2CTO, M3[0Eh])

- 22.1.7 I2C Slave Address Register (I2CSLA, M3[0Fh])

- 22.2 I2C Code Examples

- 22.1 I2C Register Descriptions

- SECTION 23: SUPPLY VOLTAGE MONITOR AND POWER CONTROL(SPECIFIC TO MAXQ2010)

- SECTION 24: UTILITY ROM (SPECIFIC TO MAXQ2010)

- APPENDIX 1: SAMPLE MAXQ2010 DEVICE INCLUDE FILE FOR MAX-IDE

- REVISION HISTORY