2 timer b 16-bit capture mode, 2 timer b 16-bit capture mode -6, Maxq family user’s guide: maxq2010 supplement – Maxim Integrated MAXQ Family Users Guide: MAXQ2010 Supplement User Manual

Page 117

MAXQ Family User’s Guide:

MAXQ2010 Supplement

21-6

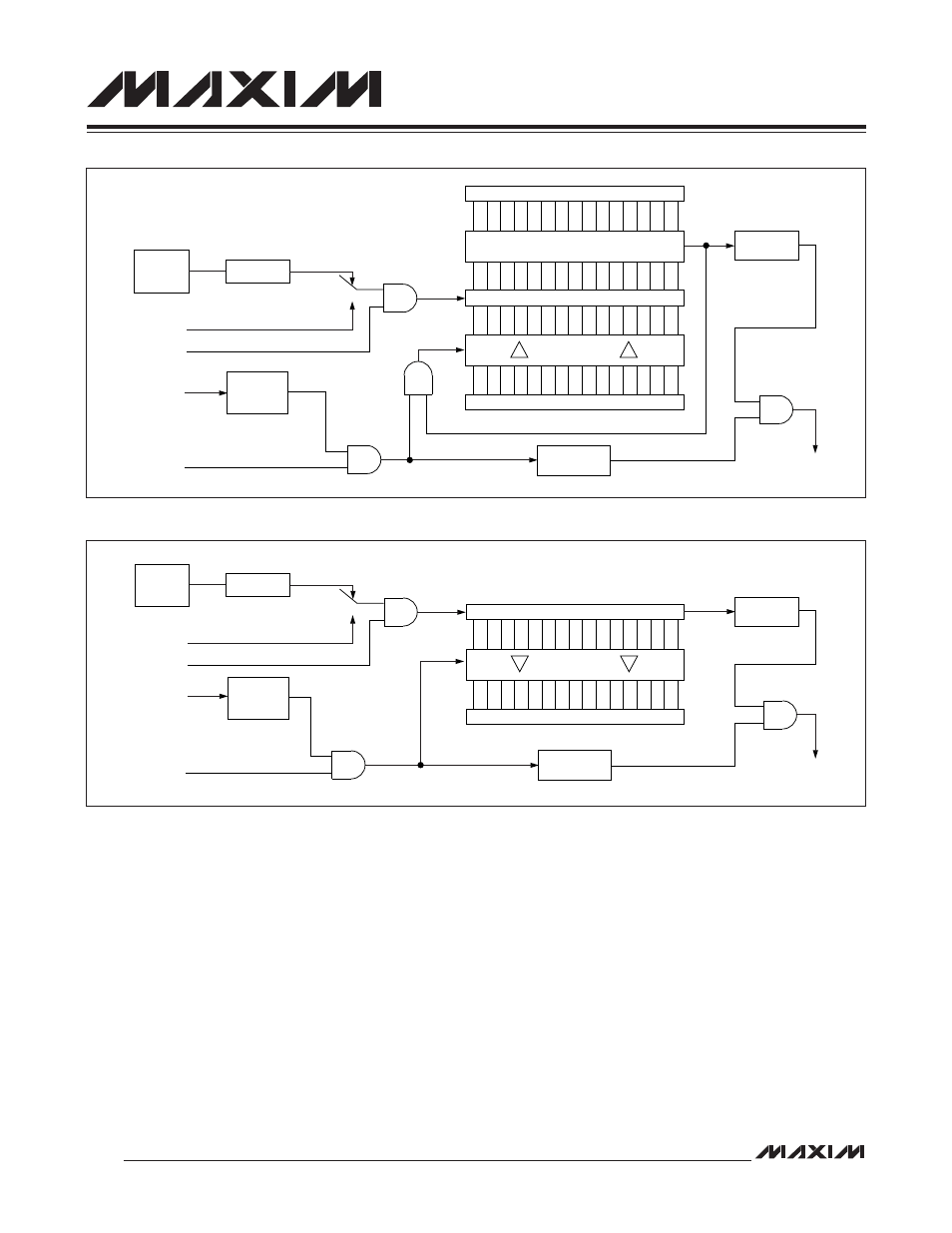

21.2.2 Timer B 16-Bit Capture Mode

The 16-bit capture mode of Timer B is configured by setting the CP/RLB bit of the control register (TBnCN.0) to 1. A

functional diagram of this mode is shown in Figure 21-2. When the timer is enabled in this mode, it begins counting

up from the value contained in the TBnV register until reaching an overflow state, i.e., FFFFh

→ 0000h; at which point

it sets the TBF flag (TBnCN.7) and continues counting upward. When the TBF flag is set, it can generate an interrupt

if enabled. This count cycle is repeated without processor intervention as long as the timer is enabled. As the count-

ing proceeds, the value in the TBnV register is captured in the capture/reload register (TBnR) if and when a high-to-

low transition occurs on the TBB pin and the EXENB bit of the control register (TBnCN.3) is set to 1. The EXFB flag

(TBnCN.6) is also set when the capture occurs, and this flag can generate an interrupt if enabled. If the EXENB bit is

cleared to 0, transitions on the TBB pin do not cause a capture event.

Figure 21-1. Timer B Autoreload Mode Block Diagram

Figure 21-2. Timer B 16-Bit Capture Mode Block Diagram

EXFB = TBnCN.6

TFB = TBnCN.7

TIMER B

INTERRUPT

15

0

15

0

RELOAD

FALLING

EDGE

TBB PIN

EXENB = TBnCN.3

TBnR

TBnV

0000h

1

TBA PIN

TRB = TBnCN.2

/CLK

COMPARE

0

SYSTEM

CLOCK

2

(2 x TBPS[2:0])

TBPS[2:0] = TBnCN[10:8]

C/TB = TBnCN.15

15

0

0

15

TBnV

TBnR

CAPTURE

0

1

TBA PIN

TRB = TBnCN.2

/CLK

TIMER B

INTERRUPT

TBB PIN

EXENB = TBnCN.3

SYSTEM

CLOCK

C/TB = TBnCN.15

EXFB = TBnCN.6

TFB = TBnCN.7

FALLING

EDGE

2

(2 x TBPS[2:0])

TBPS[2:0] = TBnCN[10:8]