1 power-on reset, 2 watchdog timer reset, 3 external reset – Maxim Integrated MAXQ Family Users Guide: MAXQ2010 Supplement User Manual

Page 22: 9 power-management features, 9 power-management features -10, Figure 2-6. power-on reset timing -10, Maxq family user’s guide: maxq2010 supplement

MAXQ Family User’s Guide:

MAXQ2010 Supplement

2-10

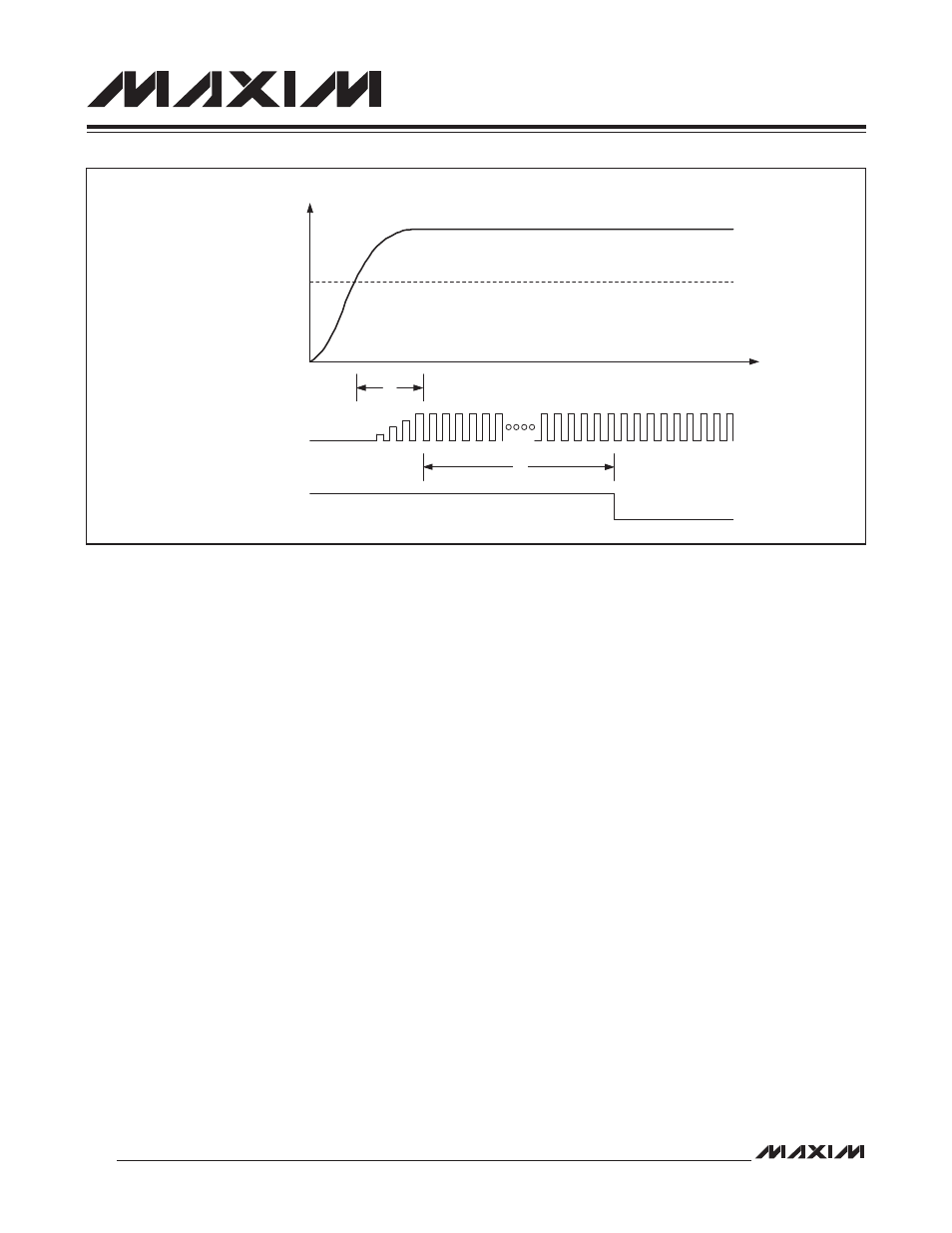

2.8.1 Power-On Reset

When power is first applied to the MAXQ2010, or when the supply voltage at V

DD

drops below the V

RST

level, the

processor is held in a power-on reset state. See Figure 2-6. For the MAXQ2010 to exit power-on reset, the following

two conditions must apply:

• The supply voltage at V

DD

is above the power-on reset level V

RST

.

• The FLL has completed 65,536 cycles (delay for power supply to stabilize).

2.8.2 Watchdog Timer Reset

The watchdog timer on the MAXQ2010 functions as described in the MAXQ Family User’s Guide.

2.8.3 External Reset

External reset through the RST input is a synchronous reset source. After the external reset low has been removed and

sampled, execution resumes following a delay of four clock cycles, as shown in Figure 2-7.

2.9 Power-Management Features

The MAXQ2010 provides the following features to assist in power management:

• Divide-by-256 (PMM) mode to reduce current consumption.

• Switchback mode to exit PMM mode automatically when rapid processing is required.

• Ultra-low-power stop mode.

• Selective regulator and brownout detection disable during stop mode.

• Selectable noise immune mode or quiet mode for 32kHz oscillator operation.

Table 2-3 shows the system registers and bits used to control power-management features. For more information, see

the register descriptions in this document and in the MAXQ Family User’s Guide.

Figure 2-6. Power-On Reset Timing

V

RST

SUPPLY AT V

DD

T1

FREQUENCY-LOCKED LOOP

INTERNAL RESET

T2

(T1 = STARTUP TIME FOR FLL)

(T2 = 65,536 FLL CYCLES, OR 7.84ms AT 8.4MHz)