1 divide-by-256 mode (pmm), 2 switchback mode, Maxq family user’s guide: maxq2010 supplement – Maxim Integrated MAXQ Family Users Guide: MAXQ2010 Supplement User Manual

Page 24

MAXQ Family User’s Guide:

MAXQ2010 Supplement

2-12

2.9.1 Divide-by-256 Mode (PMM)

In this power-management mode, all operations continue as normal, but at a reduced clock rate (the high-frequency

clock divided by 256). This power-management mode affects module clock rates as follows:

• Program execution occurs at the high-frequency clock rate divided by 256.

• The RTC module continues to operate using the 32kHz clock.

• The LCD module continues to operate using its originally selected clock, which is either the high-frequency clock

divided by 512 or the 32kHz clock, as selected by the LCCS bit (LCRA.6).

• All other functional modules (timers, USARTs, SPI) operate at the high-frequency clock rate divided by 256.

This power-management mode is entered by setting the PMME bit (CKCN.2) to 1. When PMM mode is exited (either

by clearing the PMME bit or as a result of a switchback trigger), system operation reverts to divide-by-1 mode.

2.9.2 Switchback Mode

As described in the MAXQ Family User’s Guide, switchback mode is used to provide an automatic exit from power-

management mode when a higher clock rate is required to respond to I/O, such as USART activity, SPI activity, or an

external interrupt.

Switchback mode is enabled when the SWB (CKCN.3) bit is set to 1 and the PMME (CKCN.2) bit is set to 1 (the system

is in the PMM mode). If switchback is enabled, the PMME bit is cleared (causing the system to exit power-management

mode) when any of the following conditions occur:

• An external interrupt condition occurs on an external interrupt pin and the corresponding external interrupt is enabled.

• An active-low transition occurs on the RXD0 or RXD1 pin, and the corresponding USART is enabled to receive data.

• The SBUF0 or SBUF1 register is written to transmit a byte over the corresponding USART.

• The SPIB register is written to transmit a byte with the SPI interface enabled in master mode.

• The SSEL signal is asserted low with the SPI interface enabled in slave mode.

• A START condition occurs on the I

2

C bus and the I

2

C start interrupt is triggered.

• The supply voltage drops below the supply voltage monitor (SVM) threshold, and the SVM interrupt is triggered.

• A time-of-day alarm is generated by the RTC module.

• A subsecond alarm is generated by the RTC module.

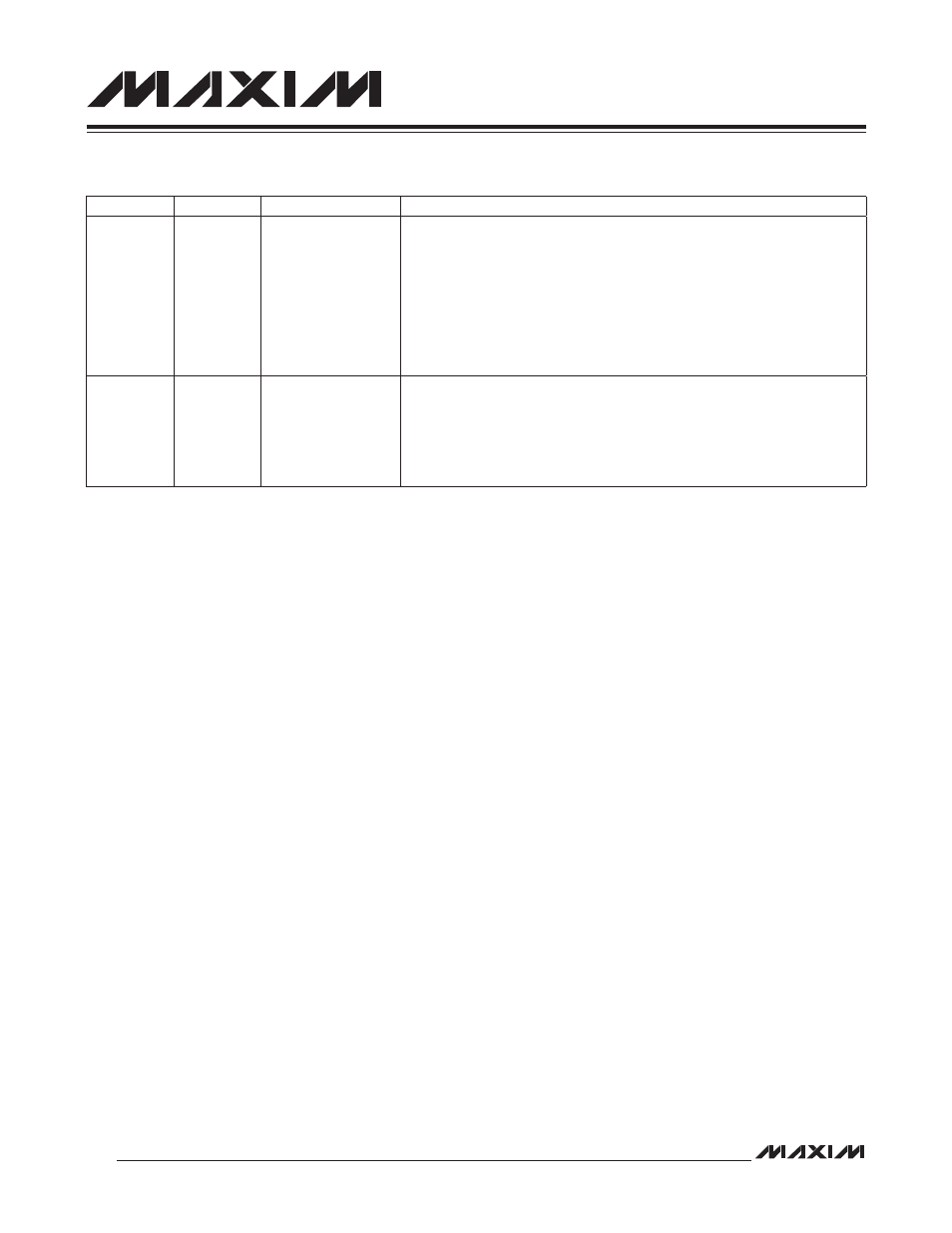

Table 2-3. System Power-Management Registers (continued)

REGISTER

ADDRESS

BIT

FUNCTION

PWCN

M0[0Fh]

[9:8]—X32KMD[1:0]

Selects operating mode of the 32kHz oscillator as follows.

00: Always operate in noise immune mode.

01: Always operate in quiet mode.

10: Operate in noise immune mode normally and in quiet mode during stop.

Wait for 32kHz oscillator warmup upon stop mode exit. (Note: This setting

should not be used on devices of rev B3 or earlier; refer to the device

errata for more details.)

11: Operate in noise immune mode normally and in quiet mode during stop.

Skip 32kHz oscillator warmup upon stop mode exit.

PWCN

M0[0Fh]

15—FREQMD

This bit is used to adjust the operating mode of the MAXQ2010 to provide

optimal current consumption based on operating frequency. Typically,

when running at a frequency of 3MHz or higher, this bit should be set to

0 to optimize current consumption. When running at a frequency under

3MHz, this bit should typically be set to 1. Refer to the “V

DD

Supply Current

vs. Clock Frequency” graph in the IC data sheet for more details.