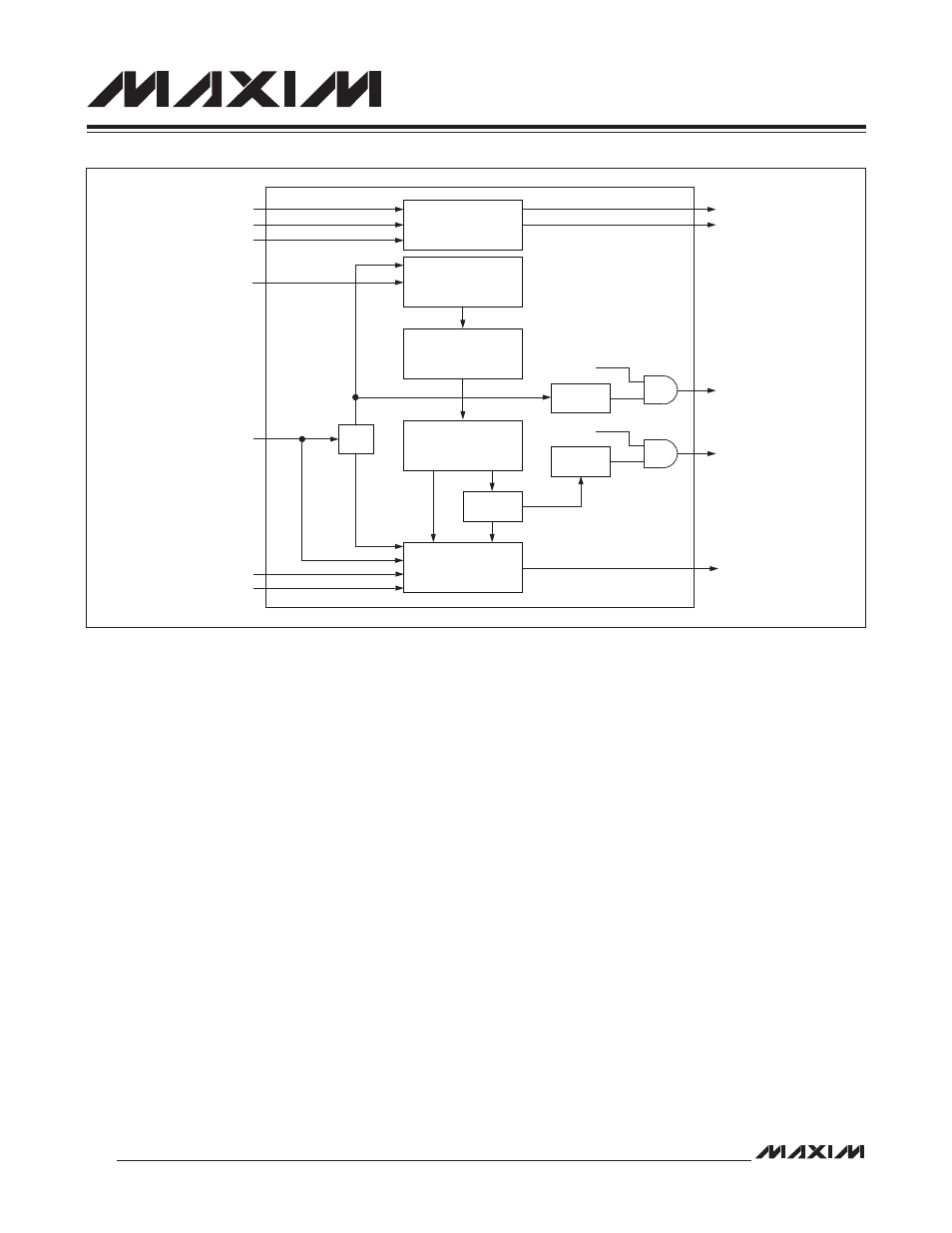

3 rtc trim operation, 3 rtc trim operation -2, Figure 14-1. rtc block diagram -2 – Maxim Integrated MAXQ Family Users Guide: MAXQ2010 Supplement User Manual

Page 64: Maxq family user’s guide: maxq2010 supplement

MAXQ Family User’s Guide:

MAXQ2010 Supplement

14-2

14.3 RTC Trim Operation

The uncompensated accuracy of the RTC is a function of the attached crystal oscillator (and its respective temperature

drift characteristics within the end system). To accommodate those applications requiring high accuracy, a digital trim

facility is made accessible to the user. The trim facility, instead of adjusting the internal capacitive load, allows extra

clocks to be inserted, removed at the 4096Hz stage in the prescaler. Four trim bits (TRM[3:0]) are used to control the

trim adjustment, and the sign bit (TSGN) designates whether pulses should be added (TSGN = 1) or subtracted (TSGN

= 0) from the prescaler count. Every 10 seconds (at the second boundary), 4K clocks can be added or subtracted

from the prescaler. See Figure 14-2.

The minimum adjustment TRM[3:0] = 01h would result in a time adjustment of 1/(4096x10) = 24.41ppm (244µs) in

10 seconds. The maximum adjustment would be achieved by programming TRM[3:0] = 0Fh. This would result in an

adjustment of 366.2ppm (3.662ms). This range of adjustment should be satisfactory to cover the temperature drift

characteristics of most 32kHz crystals over the industrial temperature range.

Normally, the prescaler counts 16 clocks of the 4K input to advance the RTSS subsecond count by 1. When TSGN

= 1, the prescaler count limit is increased by the value as indicated in RTRM[3:0]. For example, if the RTRM = 1000

0011b, instead of counting 16 clocks of the 4K input, the prescaler counts 16 + 3 = 19 of 4K clocks before advancing

the RTSS subsecond count by 1, effectively adding 732µs of delay and thus slowing down the clock. See Figure 14-3.

Similarly, when TSGN = 0, the prescaler count limit is decremented by the value specified in RTRM[3:0]. For example,

if the RTRM = 0000 0011b, instead of counting 16 clocks of the 4K input, the prescaler counts 16 - 3 = 13 of the 4K

clocks before advancing the RTSS subsecond count by 1, effectively advancing the RTC ahead by 732µs and hence

speeding up the clock. See Figure 14-4.

Figure 14-1. RTC Block Diagram

RTC

CONTROL

COMPENSATION

PRESCALER

RTSS

SQE

FT[1:O]

32K_CLK

RTRIM

RTCE

RDYE

WE

CLOCK OUTPUT

GENERATION

RSSA

COMPARE

BUSY

RDY

SQW

RAS

RTS

ADE

ALDF

ASE

ALSF

/8