3 port 2 direction register (pd2, m0[12h]), 4 port 3 direction register (pd3, m0[13h]), 5 port 4 direction register (pd4, m1[10h]) – Maxim Integrated MAXQ Family Users Guide: MAXQ2010 Supplement User Manual

Page 43: Maxq family user’s guide: maxq2010 supplement

MAXQ Family User’s Guide:

MAXQ2010 Supplement

6-5

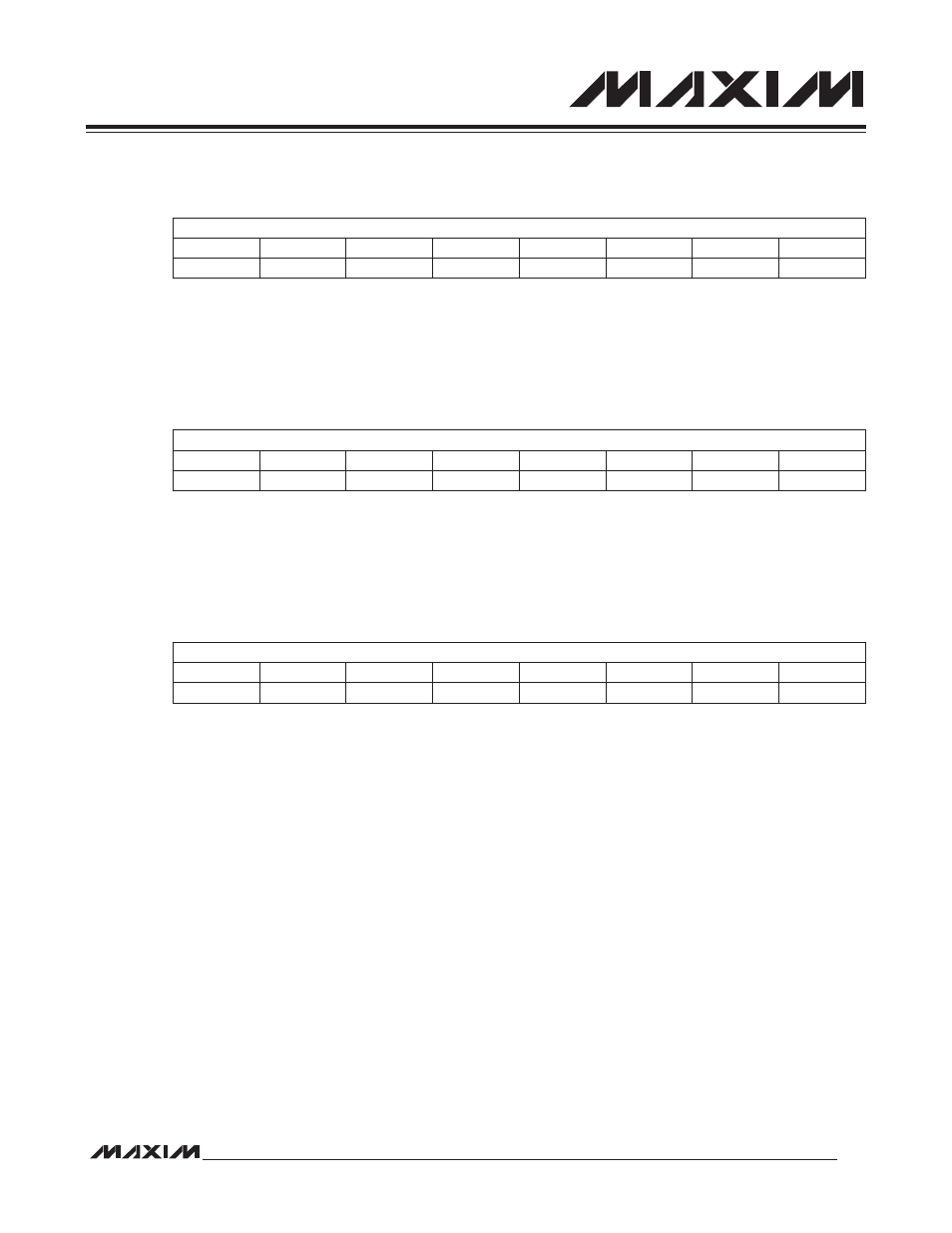

6.1.3 Port 2 Direction Register (PD2, M0[12h])

Each of the bits in this register controls the input/output direction of a port pin (P2.0 to P2.7) as follows:

0 = The port pin is in input mode, either with a weak pullup (if PO = 1) or three-stated (if PO = 0).

1 = The port pin is in output mode, with the output level to drive given by PO.

6.1.4 Port 3 Direction Register (PD3, M0[13h])

Each of the bits in this register controls the input/output direction of a port pin (P3.0 to P3.7) as follows:

0 = The port pin is in input mode, either with a weak pullup (if PO = 1) or three-stated (if PO = 0).

1 = The port pin is in output mode, with the output level to drive given by PO.

6.1.5 Port 4 Direction Register (PD4, M1[10h])

Each of the bits in this register controls the input/output direction of a port pin (P4.0 to P4.7) as follows:

0 = The port pin is in input mode, either with a weak pullup (if PO = 1) or three-stated (if PO = 0).

1 = The port pin is in output mode, with the output level to drive given by PO.

Bit #

7

6

5

4

3

2

1

0

Name

PD2

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

PD3

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

PD4

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw