Maxq family user’s guide: maxq2010 supplement, Table 18-1. instruction set summary (continued) – Maxim Integrated MAXQ Family Users Guide: MAXQ2010 Supplement User Manual

Page 82

MAXQ Family User’s Guide:

MAXQ2010 Supplement

18-2

Note 1: The active accumulator (Acc) is not allowed as the src in operations where it is the implicit destination.

Note 2: Only module 8 and modules 0 to 5 (when implemented for a given product) are supported by these single-cycle bit opera-

tions. Potentially affects C or E if PSF register is the destination. Potentially affects S and/or Z if AP or APC is the destination.

Note 3: The terms Acc and A[AP] can be used interchangeably to denote the active accumulator.

Note 4: Any index represented by or found inside [ ] brackets is considered variable, but required.

Note 5: The active accumulator (Acc) is not allowed as the dst if A[AP] is specified as the src.

Note 6: The ‘{L/S}’ prefix is optional.

Note 7: Instructions that attempt to simultaneously push/pop the stack (e.g. PUSH @SP--, PUSH @SPI--, POP @++SP, POPI

@++SP) or modify SP in a conflicting manner (e.g., MOVE SP, @SP--) are invalid.

Note 8: Special cases: If ‘MOVE APC, Acc’ sets the APC.CLR bit, AP is cleared, overriding any autoinc/dec/modulo operation

specified for AP. If ‘MOVE AP, Acc’ causes an autoinc/dec/modulo operation on AP, this overrides the specified data

transfer (i.e., Acc is not transferred to AP).

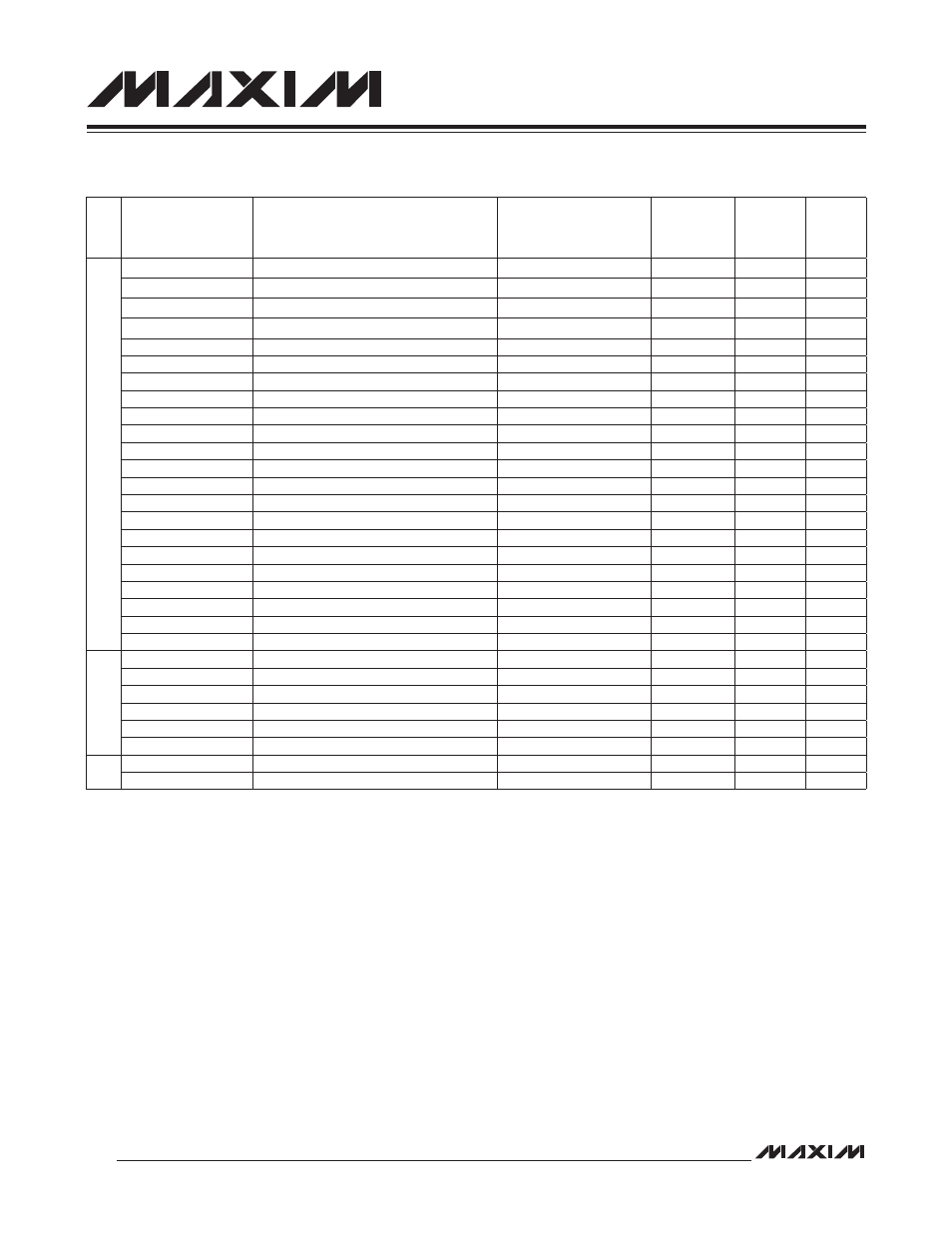

Table 18-1. Instruction Set Summary (continued)

MNEMONIC

DESCRIPTION

16-BIT INSTRUCTION

WORD

STATUS

BITS

AFFECTED

AP

INC/DEC NOTES

BRANCHING

{L/S}JUMP src

IP

← IP + src or src

f000 1100 ssss ssss

6

{L/S}JUMP C, src

If C=1, IP

← (IP + src) or src

f010 1100 ssss ssss

6

{L/S}JUMP NC, src

If C=0, IP

← (IP + src) or src

f110 1100 ssss ssss

6

{L/S}JUMP Z, src

If Z=1, IP

← (IP + src) or src

f001 1100 ssss ssss

6

{L/S}JUMP NZ, src

If Z=0, IP

← (IP + src) or src

f101 1100 ssss ssss

6

{L/S}JUMP E, src

If E=1, IP

← (IP + src) or src

0011 1100 ssss ssss

6

{L/S}JUMP NE, src

If E=0, IP

← (IP + src) or src

0111 1100 ssss ssss

6

{L/S}JUMP S, src

If S=1, IP

← (IP + src) or src

f100 1100 ssss ssss

6

{L/S}DJNZ LC[n], src If --LC[n] <> 0, IP← (IP + src) or src

f10n 1101 ssss ssss

6

{L/S}CALL src

@++SP

← IP+1; IP ← (IP+src) or src

f011 1101 ssss ssss

6, 7

RET

IP

← @SP--

1000 1100 0000 1101

RET C

If C=1, IP

← @SP--

1010 1100 0000 1101

RET NC

If C=0, IP

← @SP--

1110 1100 0000 1101

RET Z

If Z=1, IP

← @SP--

1001 1100 0000 1101

RET NZ

If Z=0, IP

← @SP--

1101 1100 0000 1101

RET S

If S=1, IP

← @SP--

1100 1100 0000 1101

RETI

IP

← @SP-- ; INS← 0

1000 1100 1000 1101

RETI C

If C=1, IP

← @SP-- ; INS← 0

1010 1100 1000 1101

RETI NC

If C=0, IP

← @SP-- ; INS← 0

1110 1100 1000 1101

RETI Z

If Z=1, IP

← @SP-- ; INS← 0

1001 1100 1000 1101

RETI NZ

If Z=0, IP

← @SP-- ; INS← 0

1101 1100 1000 1101

RETI S

If S=1, IP

← @SP-- ; INS← 0

1100 1100 1000 1101

DATA

TRANSFER

XCH (MAXQ20 only) Swap Acc bytes

1000 1010 1000 1010

S

Y

XCHN

Swap nibbles in each Acc byte

1000 1010 0111 1010

S

Y

MOVE dst, src

dst

← src

fddd dddd ssss ssss

C, S, Z, E

(Note 8)

7, 8

PUSH src

@++SP

← src

f000 1101 ssss ssss

7

POP dst

dst

← @SP--

1ddd dddd 0000 1101

C, S, Z, E

7

POPI dst

dst

← @SP-- ; INS ← 0

1ddd dddd 1000 1101

C, S, Z, E

7

CMP src

E

← (Acc = src)

f111 1000 ssss ssss

E

NOP

No operation

1101 1010 0011 1010