Speed control - regulator, Speed control - regulator (2 ms) – Rockwell Automation 1756-DMF30 ControlLogix Drive Module User Manual

Page 84

Publication 1756-UM522B-EN-P - February 2003

B-4 1756-DMD30 Specific Information

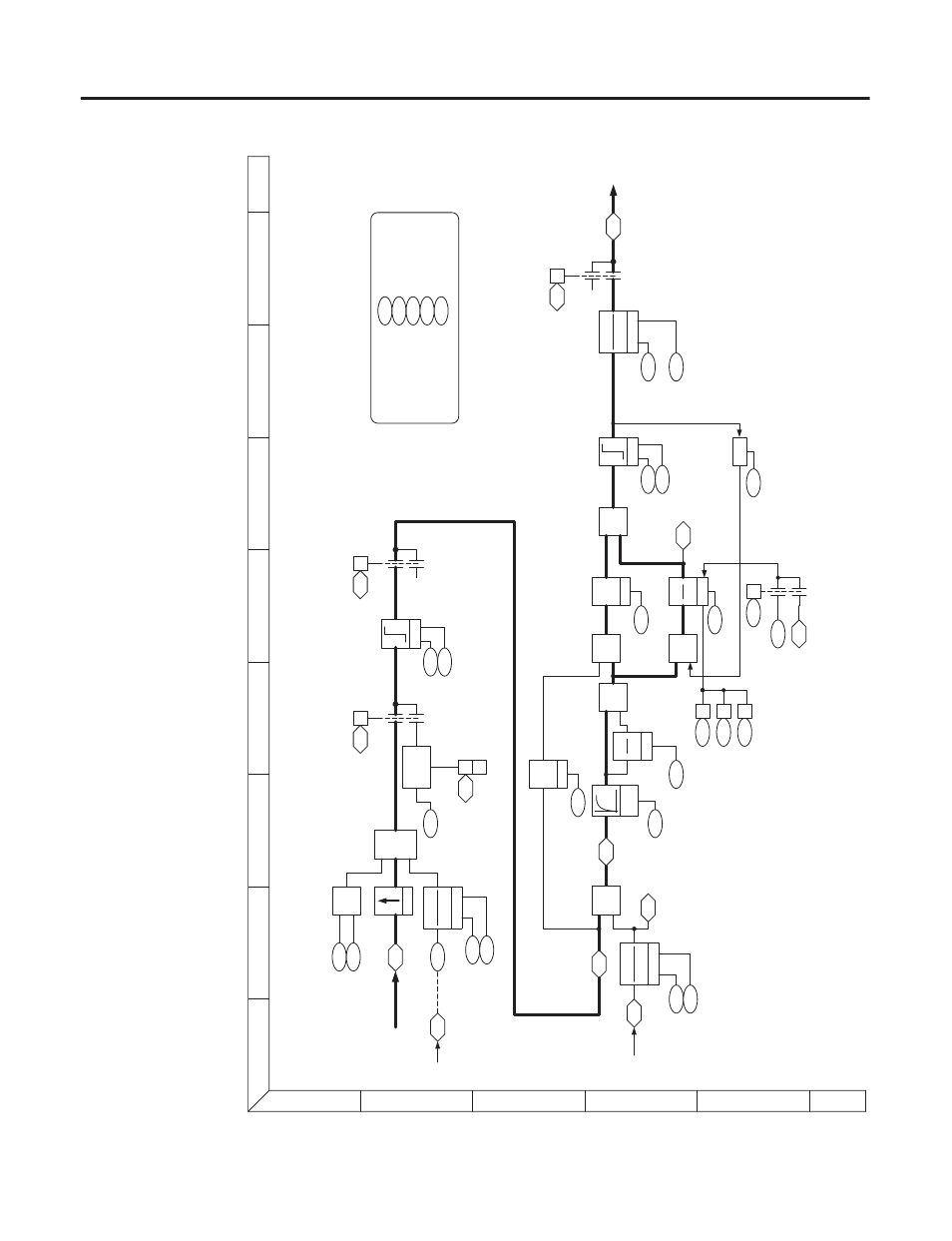

Speed Control - Regulator

Spd Reg BW

Spd Reg Damping

SpdReg P Gain Mx

Motor Iner

tia

To

tal Iner

tia

90

92

91

2190

2189

set par

am 90 = 0

to man

ually adjust

par

am 81 & 82

*

Lead Lag

(kn * s) + wn

s + wn

25

26

22

+

X

23

24

0

Au

totune

Bypass

19

157

5

8

157

04

30

31

Lead Lag

(kn * s) + wn

s + wn

93

94

89

+

85

84

81

82

80

01

153

12

+

102

103

95

96

157

08

0

86

Speed Control - Regulator

(2 ms)

Droop

47

318

301

71

300

100

101

302

Ovr Smpl

4x

0

1

157

06

0

Logic Ctr

l State

Atune Spd Ref

Limit

Logic Ctr

l State

(Inr

ta Tst

En)

Logic Ctr

l State

(CurrLim Stop)

Speed T

rim

3

SpdT

rim 3 Scale

Spd T

rim1

SpdRef

Speed T

rim

2

ST

ri

m2 Filt Gain

SpdT

ri

m2 Filt BW

Ser

v

oLc

k

ks

s

P Gain

kp

I Gain

ki

s

80

02

80

03

Limit

Spd Reg P Gain

Spd Reg I Gain

0

1

87

303

Spd Reg P

os Lim

Spd Reg Neg Lim

Lead Lag

(kn * s) + wn

s + wn

F

eedFwd

nff

SReg FB Filt Gain

SReg FB Filt BW

Filtered SpdFdbk

Motor Spd Fdbk

Motor Speed Ref

Speed Error

SpdReg AntiBc

kup

Spd Err Filt BW

Ser

v

o

Loc

k Gain

Control Options

(Jog -NoInteg)

Speed Reg Ctr

l

(Integ Hold)

Speed Reg Ctr

l

(Integ Reset)

Speed Reg Ctr

l

(Preset Sel)

SReg T

orq

Preset

Motor T

orque

Ref

Spd Reg Droop

0

1

SRegOut FiltGain

SReg Out Filt BW

Logic Ctr

l State

(Spd Reg En)

Spd Reg PI Out

Po

sit Spd Output

*

from Speed Control

- Ref

erence [2H4]

from P

osition

Control [5H3]

to T

orque

Control

[8B1]

2

nd

Order

LP

ass

Filter

SpdReg Integ Out

-

+

+

-

+

-

1

2

3

4

5

6

B

A

D

C

F

E

H

G

I

(J Tst

FulSpd)

(Spd Reg En)

1

from F

eedbac

k [9H2]