Intel 253666-024US User Manual

Page 247

Vol. 2A 3-201

INSTRUCTION SET REFERENCE, A-M

CVTPD2PS—Convert Packed Double-Precision Floating-Point Values to Packed Single-

Precision Floating-Point Values

CVTPD2PS—Convert Packed Double-Precision Floating-Point Values to

Packed Single-Precision Floating-Point Values

Description

Converts two packed double-precision floating-point values in the source operand

(second operand) to two packed single-precision floating-point values in the destina-

tion operand (first operand).

The source operand can be an XMM register or a 128-bit memory location. The desti-

nation operand is an XMM register. The result is stored in the low quadword of the

destination operand, and the high quadword is cleared to all 0s. When a conversion

is inexact, the value returned is rounded according to the rounding control bits in the

MXCSR register.

In 64-bit mode, use of the REX.R prefix permits this instruction to access additional

registers (XMM8-XMM15).

Operation

DEST[31:0] ← Convert_Double_Precision_To_Single_Precision_Floating_Point(SRC[63:0]);

DEST[63:32] ← Convert_Double_Precision_To_Single_Precision_

Floating_Point(SRC[127:64]);

DEST[127:64] ← 0000000000000000H;

Intel C/C++ Compiler Intrinsic Equivalent

CVTPD2PS

__m128 _mm_cvtpd_ps(__m128d a)

SIMD Floating-Point Exceptions

Overflow, Underflow, Invalid, Precision, Denormal.

Protected Mode Exceptions

#GP(0)

For an illegal memory operand effective address in the CS, DS,

ES, FS or GS segments.

If a memory operand is not aligned on a 16-byte boundary,

regardless of segment.

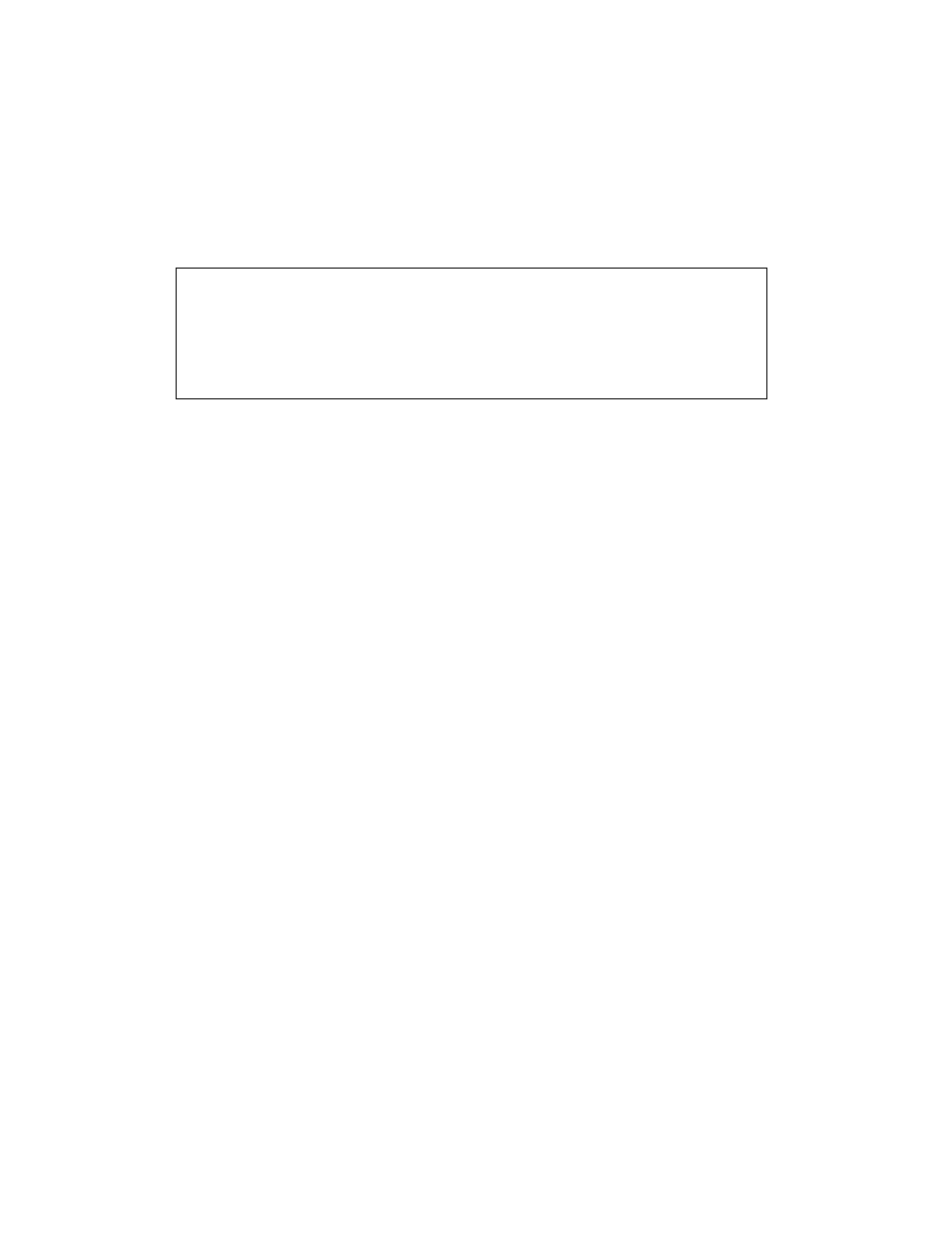

Opcode

Instruction

64-Bit

Mode

Compat/

Leg Mode

Description

66 0F 5A /r

CVTPD2PS xmm1,

xmm2/m128

Valid

Valid

Convert two packed double-

precision floating-point values in

xmm2/m128 to two packed single-

precision floating-point values in

xmm1.