Artesyn CPCI-6200 Installation and Use (May 2015) User Manual

Page 195

Memory Maps and Addresses

CPCI-6200 Installation and Use (6806800J66E)

195

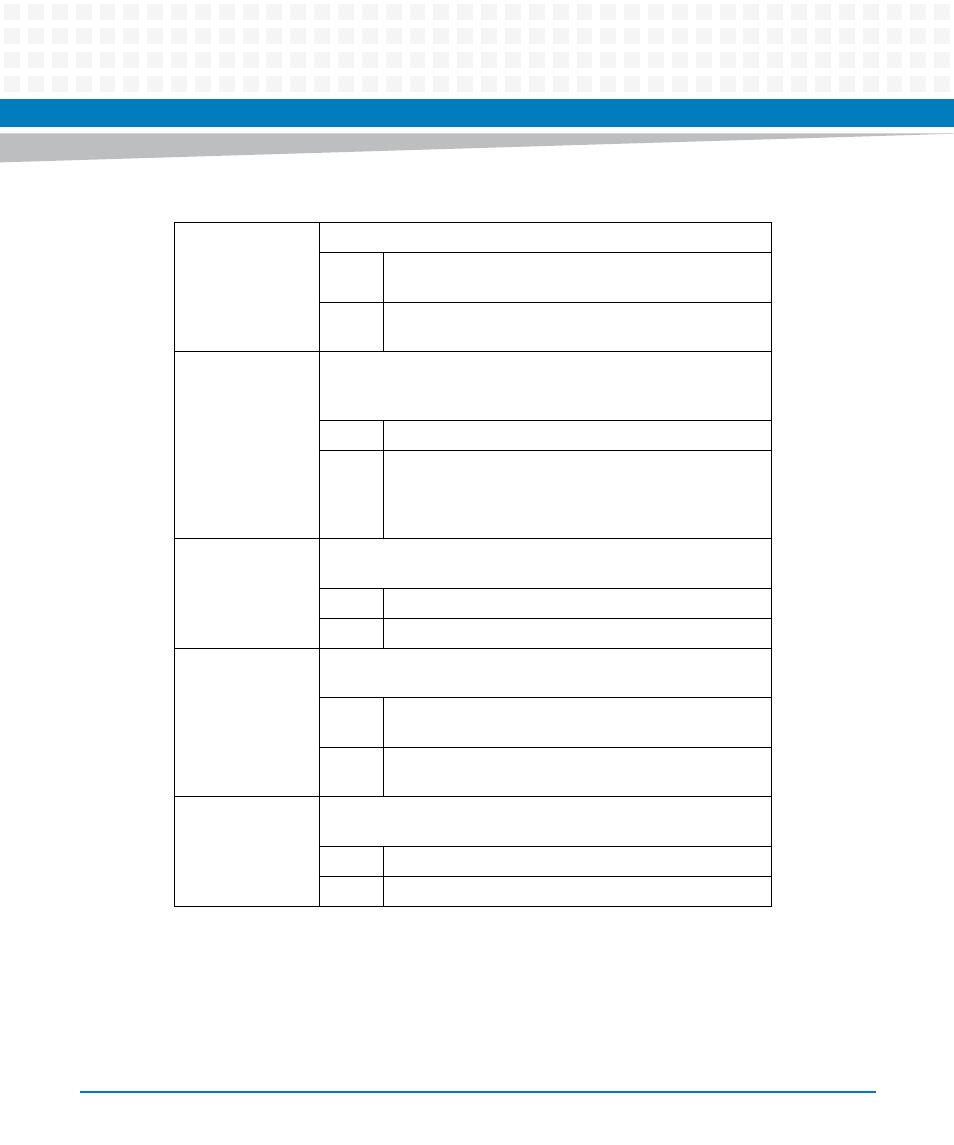

MAP_SEL

Memory Map Select

1

Flash memory boot block A is selected and mapped to

the highest address. See

.

0

Flash memory map is controlled by the Flash Boot Block

Select switch.

F_WP_SW

Software flash bank write protect. This bit provides software-

controlled protection against inadvertent writes to the flash

memory devices.

1

Flash is write-protected.

0

Flash bank is not write-protected, if the HW write-

protect bit is not set. This bit is set during reset and

must be cleared by the system software to enable

writing of the flash devices.

F_WP_HW

Hardware flash bank write protect switch status reflects the

current state of the FLASH BANK WP switch.

1

Flash is write-protected.

0

Flash is not write-protected.

FBT_BLK_SEL

Flash Boot Block Select. This reflects the current state of the

BOOT BLOCK B SELECT switch.

1

Boot block B is selected and mapped to the highest

address. See

.

0

Boot block A is selected and mapped to the highest

address. See

.

FLASH_RDY

Flash Ready. This bit provides the current state of the flash

devices’ Ready/Busy# pins.

1

FLASH is ready.

0

FLASH is not ready.

Table 8-12 NOR Flash Control/Status Register Field Definition (continued)