Altpll_reconfig counter settings, Altpll_reconfig counter settings -7 – Altera MAX 10 Clocking and PLL User Manual

Page 83

Port Name

Condition

Description

pll_scanclkena

Optional

This port acts as a clock enable for the

scanclk

port on

the PLL to be reconfigured.

Reconfiguration begins on the first rising edge of

pll_

scanclk

after

pll_scanclkena

assertion. On the first

falling edge of

pll_scanclk

, after the deassertion of the

pll_scanclkena

signal, the IP core stops scanning data

to the PLL.

pll_scandata

Required

Drives the

scandata

port on the PLL to be reconfigured.

This output port from the IP core holds the scan data

input to the PLL for the dynamically reconfigurable bits.

The

pll_scandata

port sends

scandata

to the PLL. Any

activity on this port can only be observed when the

reconfig

signal is asserted.

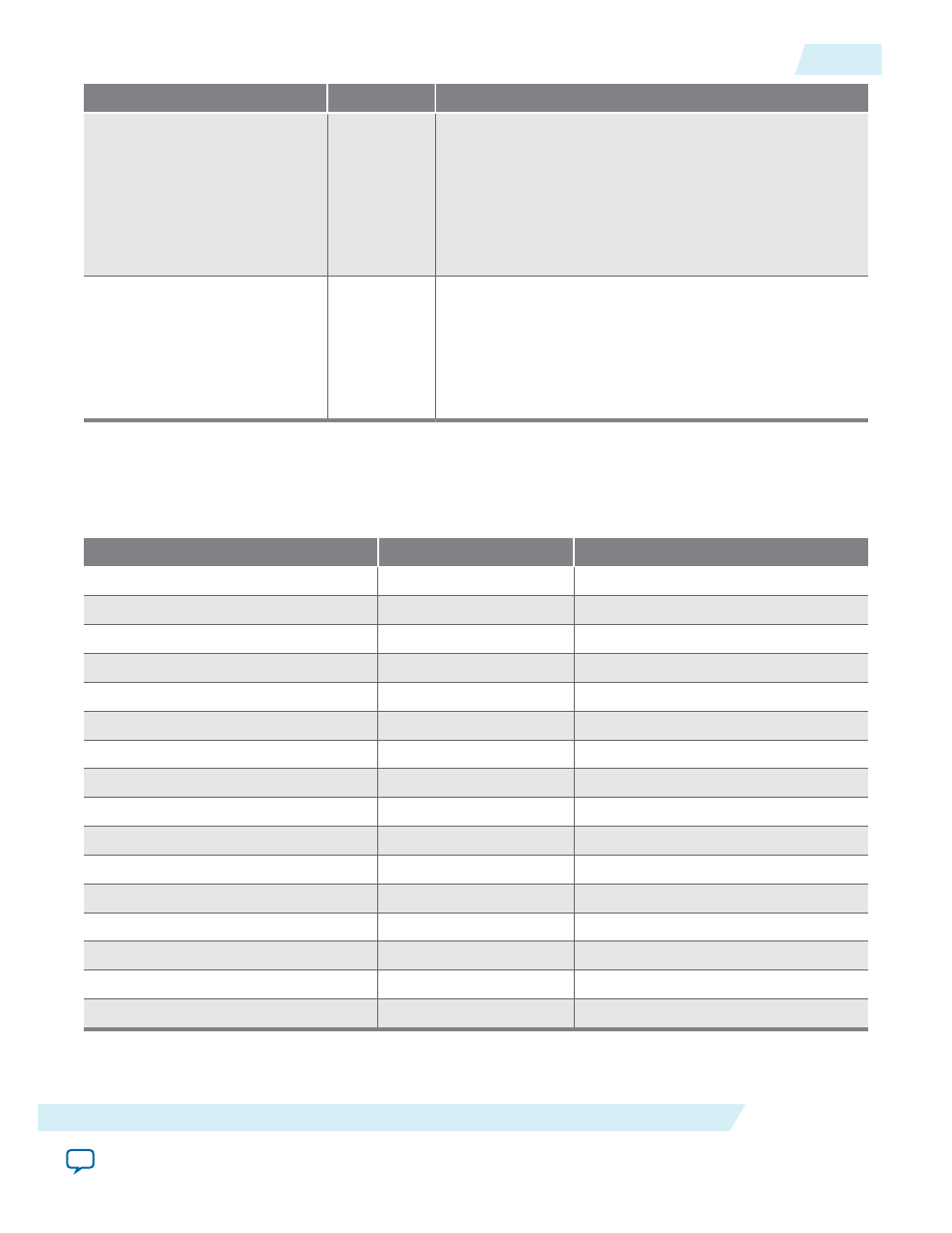

ALTPLL_RECONFIG Counter Settings

Table 7-4:

counter_type[3..0]

Settings for MAX 10 Devices

Counter Selection

Binary

Decimal

N

0000

0

M

0001

1

CP/LF

0010

2

VCO

0011

3

C0

0100

4

C1

0101

5

C2

0110

6

C3

0111

7

C4

1000

8

Illegal value

1001

9

Illegal value

1010

10

Illegal value

1011

11

Illegal value

1100

12

Illegal value

1101

13

Illegal value

1110

14

Illegal value

1111

15

UG-M10CLKPLL

2015.05.04

ALTPLL_RECONFIG Counter Settings

7-7

ALTPLL_RECONFIG IP Core References

Altera Corporation