Pll cascading, Pll-to-pll cascading, Counter-to-counter cascading – Altera MAX 10 Clocking and PLL User Manual

Page 32: Pll reconfiguration, Pll cascading -26, Pll reconfiguration -26

If

inclk0

and

inclk1

have different frequencies and are always running, the minimum amount of time

for which

clkswitch

signal is high must be greater than or equal to three of the slower-frequency

inclk0

and

inclk1

cycles.

PLL Cascading

Related Information

on page 3-3

PLL-to-PLL Cascading

Two PLLs are cascaded to each other through the clock network. If your design cascades PLLs, the source

(upstream) PLL must have a low-bandwidth setting and the destination (downstream) PLL must have a

high-bandwidth setting.

Counter-to-Counter Cascading

The MAX 10 PLLs support post-scale counter cascading to create counters larger than 512. This is

implemented by feeding the output of one

C

counter into the input of the next

C

counter.

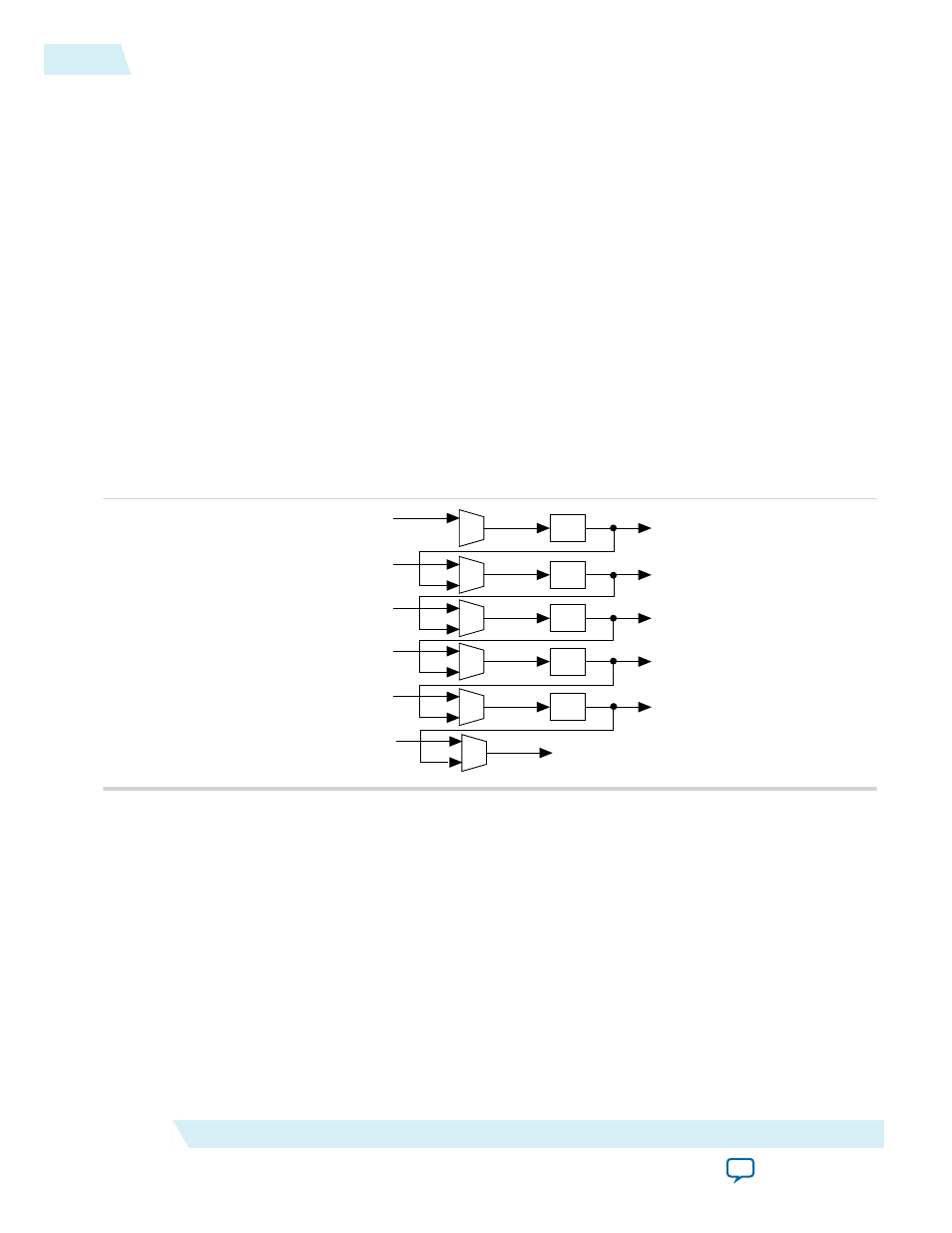

Figure 2-23: Counter-to-Counter Cascading

C0

C1

C2

C3

C4

VCO Output

VCO Output

VCO Output

VCO Output

VCO Output

VCO Output

When cascading counters to implement a larger division of the high-frequency VCO clock, the cascaded

counters behave as one counter with the product of the individual counter settings.

For example, if

C0

= 4 and

C1

= 2, the cascaded value is

C0

x

C1

= 8.

The Quartus II software automatically sets all the post-scale counter values for cascading in the configura‐

tion file. Post-scale counter cascading cannot be performed using PLL reconfiguration.

PLL Reconfiguration

The PLLs use several divide counters and different VCO phase taps to perform frequency synthesis and

phase shifts. In MAX 10 PLLs, you can reconfigure both counter settings and phase shift the PLL output

clock in real time. You can also change the charge pump and loop filter components, which dynamically

affects the PLL bandwidth.

2-26

PLL Cascading

UG-M10CLKPLL

2015.05.04

Altera Corporation

MAX 10 Clocking and PLL Architecture and Features