Altpll ports and signals, Altpll ports and signals -6 – Altera MAX 10 Clocking and PLL User Manual

Page 72

Parameter

Value

Description

Clock duty cycle (%)

—

Set the duty cycle of the output clock signal.

Per Clock Feasibility

Indicators

—

Indicate output clocks that contain unachievable

settings.

The output clock name in red is the name of the clock

with unachievable settings. The clock listed in green has

no settings issues, and the grayed-out names are the

unselected output clocks. You must adjust the requested

settings for the affected output clocks to resolve the

warning messages.

The ALTPLL IP core parameter editor calculates the simplest fraction, and displays it in the actual settings

column. You can use the copy button to copy values from the actual settings to the requested settings.

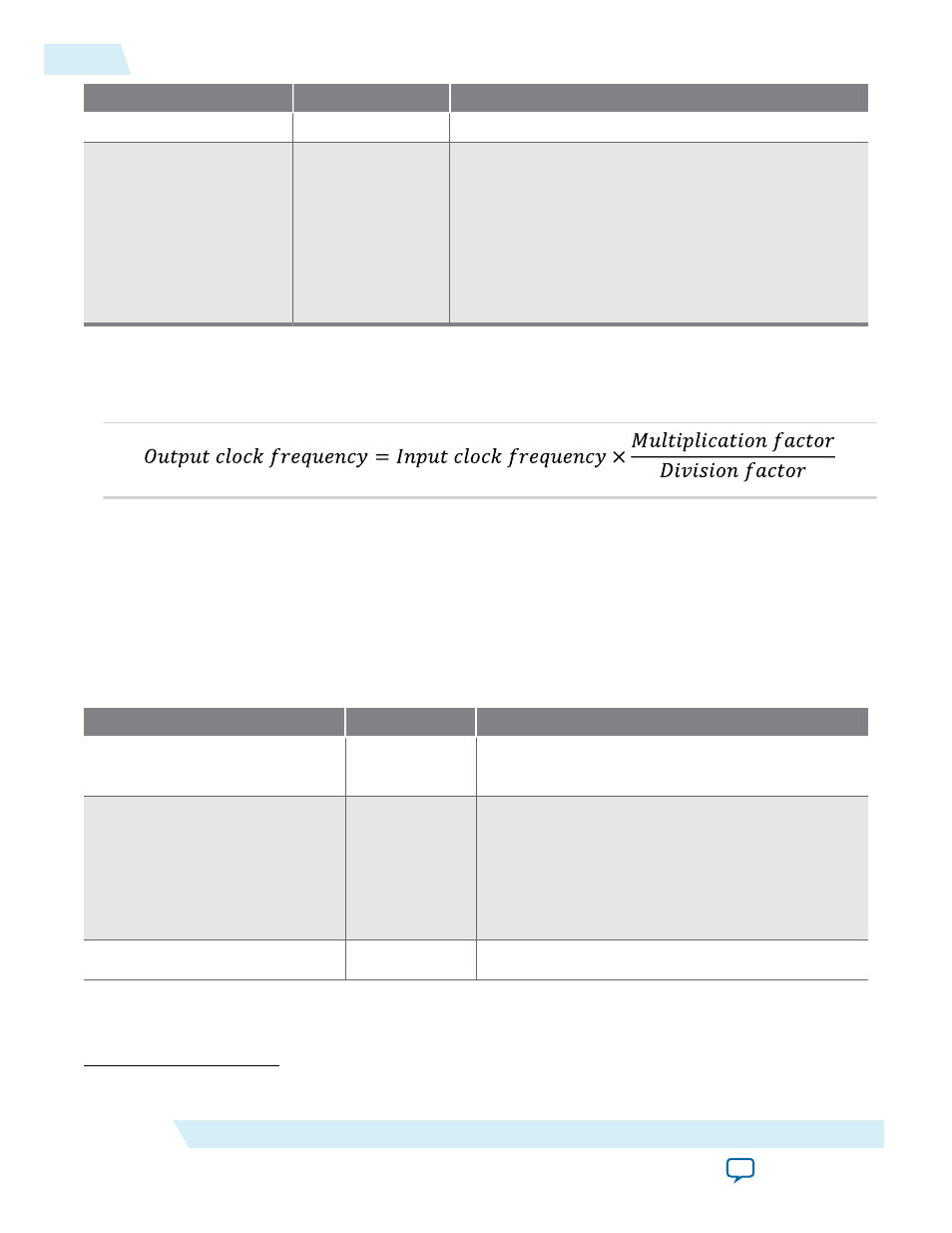

Figure 6-1: PLL Output Clock Frequency

For example, if the input clock frequency is 100 MHz, and the requested multiplication and division

factors are 205 and 1025 respectively, the output clock frequency is calculated as 100 × 205/1025=20 MHz.

The actual settings reflect the simplest fraction—the actual multiplication factor is 1, and the actual

division factor is 5.

ALTPLL Ports and Signals

Table 6-7: ALTPLL Input Ports for MAX 10 Devices

Port Name

(10)

Condition

Description

areset

Optional

Resets all counters to initial values, including the

GATE_LOCK_COUNTER

parameter.

clkswitch

Optional

The control input port to dynamically toggle

between clock input ports (

inclk0

and

inclk1

ports), or to manually override the automatic clock

switchover.

You should create the

clkswitch

port if only the

inclk1

port is created.

configupdate

Optional

Dynamic full PLL reconfiguration.

(10)

Replace brackets, [], in the port name with integer to get the exact name. For example,

inclk0

and

inclk1

.

6-6

ALTPLL Ports and Signals

UG-M10CLKPLL

2014.12.15

Altera Corporation

ALTPLL IP Core References