Dynamic phase configuration implementation – Altera MAX 10 Clocking and PLL User Manual

Page 53

Dynamic Phase Configuration Implementation

To perform one dynamic phase shift step, perform the following steps:

1. Set

PHASEUPDOWN

and

PHASECOUNTERSELECT

as required.

2. Assert

PHASESTEP

for at least two

SCANCLK

cycles. Each

PHASESTEP

pulse allows one phase shift.

3. Deassert

PHASESTEP

after

PHASEDONE

goes low.

4. Wait for

PHASEDONE

to go high.

5. Repeat steps 1 through 4 as many times as required to perform multiple phase shifts.

PHASEUPDOWN

and

PHASECOUNTERSELECT

signals are synchronous to

SCANCLK

and must meet the t

su

and t

h

requirements with respect to the

SCANCLK

edges.

You can repeat dynamic phase-shifting indefinitely. For example, in a design where the VCO frequency is

set to 1,000 MHz and the output clock frequency is set to 100 MHz, performing 40 dynamic phase shifts

(each one yields 125 ps phase shift) results in shifting the output clock by 180º, which is a phase shift of 5

ns.

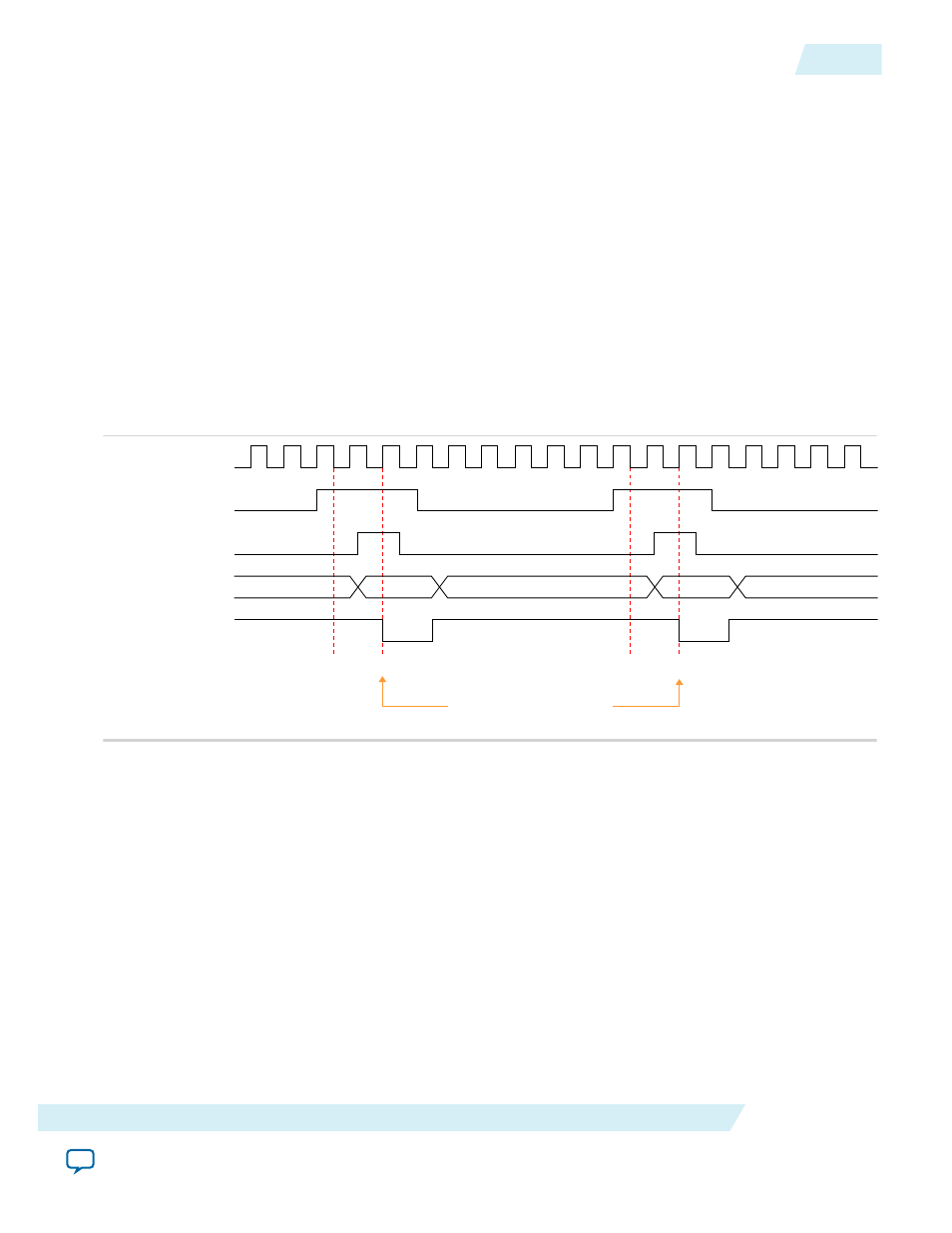

Figure 4-9: Dynamic Phase Shift Timing Diagram

PHASEDONE goes low

synchronous with SCANCLK

SCANCLK

PHASESTEP

PHASEUPDOWN

PHASECOUNTERSELECT

PHASEDONE

a

b

c

d

The

PHASESTEP

signal is latched on the negative edge of

SCANCLK

(a,c) and must remain asserted for at

least two

SCANCLK

cycles. Deassert

PHASESTEP

after

PHASEDONE

goes low.

On the second

SCANCLK

rising edge (b,d) after

PHASESTEP

is latched, the values of

PHASEUPDOWN

and

PHASECOUNTERSELECT

are latched. The PLL starts dynamic phase-shifting for the specified counters and in

the indicated direction.

The

PHASEDONE

signal is deasserted synchronous to

SCANCLK

at the second rising edge (b,d) and remains

low until the PLL finishes dynamic phase-shifting. Depending on the VCO and

SCANCLK

frequencies,

PHASEDONE

low time may be greater than or less than one

SCANCLK

cycle.

You can perform another dynamic phase-shift after the

PHASEDONE

signal goes from low to high. Each

PHASESTEP

pulse enables one phase shift. The

PHASESTEP

pulses must be at least one

SCANCLK

cycle apart.

Related Information

•

on page 2-20

•

Dynamic Phase Configuration Parameter Settings

Provides more information about the ALTPLL IP core parameter settings in the Quartus II software.

UG-M10CLKPLL

2015.05.04

Dynamic Phase Configuration Implementation

4-15

MAX 10 Clocking and PLL Implementation Guides

Altera Corporation