Pll dynamic reconfiguration parameter settings, Dynamic phase configuration parameter settings, Pll dynamic reconfiguration parameter settings -4 – Altera MAX 10 Clocking and PLL User Manual

Page 70: Dynamic phase configuration parameter settings -4

•

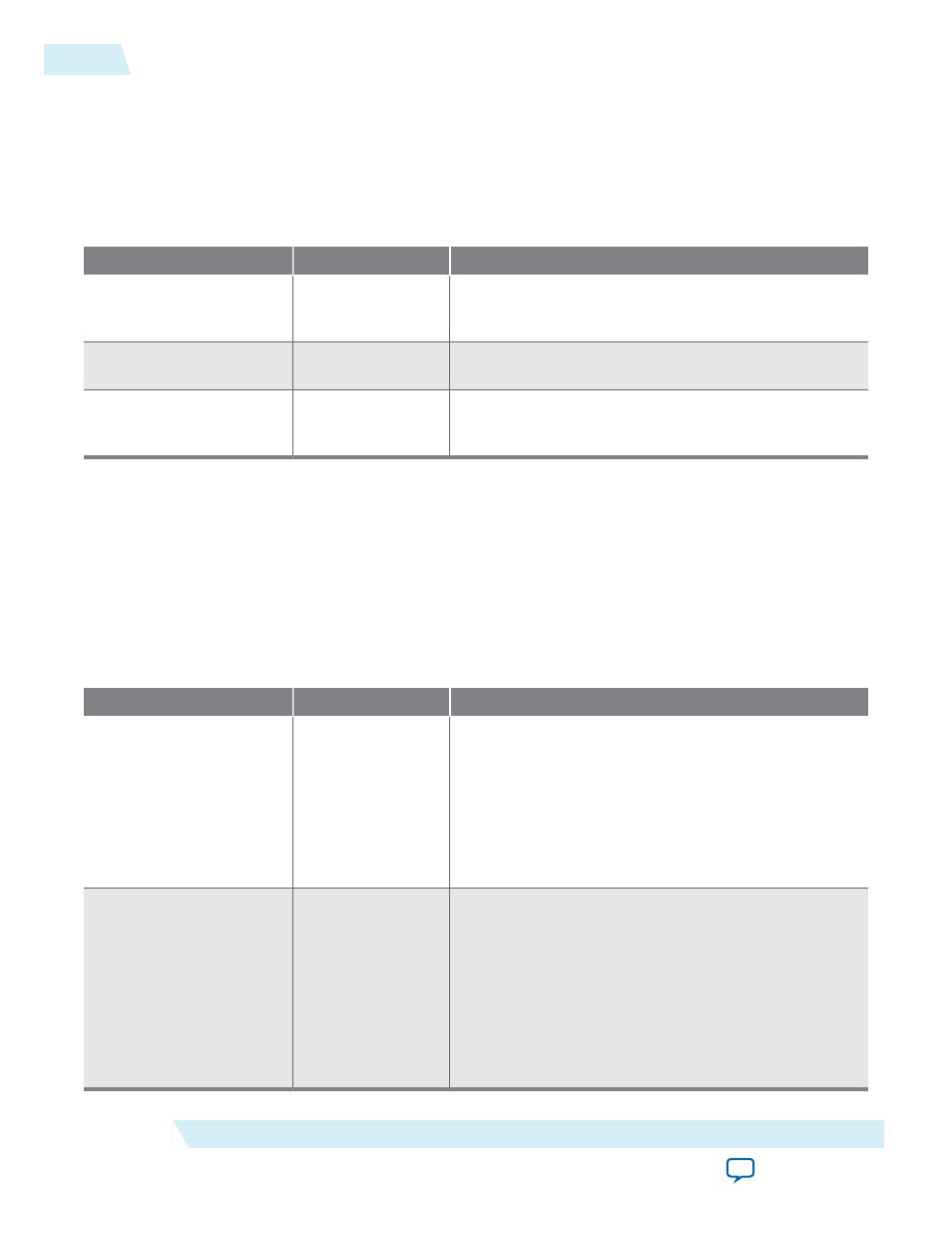

PLL Dynamic Reconfiguration Parameter Settings

The parameter settings for the normal dynamic reconfiguration scheme are located on the PLL Reconfi‐

guration page of the ALTPLL IP core parameter editor.

Table 6-4: PLL Dynamic Reconfiguration Parameter Editor Settings

Parameter

Value

Description

Create optional inputs

for dynamic reconfigu‐

ration

On or Off

Turn on this option to enable all the PLL reconfigura‐

tion ports for this instantiation—

scanclk

,

scanclkena

,

scandata

,

scandone

,

scandataout

, and

configupdate

.

Initial Configuration

File

—

Specify the location of the configuration file that is used

to initialize the ALTPLL_RECONFIG IP core.

Additional Configura‐

tion File(s)

—

Specify additional configuration file. This file might

contain additional settings for the PLL, or might be

used to initialize the ALTPLL_RECONFIG IP core.

Related Information

•

on page 2-26

•

Dynamic Phase Configuration Implementation

Dynamic Phase Configuration Parameter Settings

The parameter settings to enable the dynamic phase configuration feature are located on the PLL

Reconfiguration page of the ALTPLL IP core parameter editor.

Table 6-5: Dynamic Phase Configuration Parameter Editor Settings

Parameter

Value

Description

Create optional inputs

for dynamic phase

reconfiguration

On or Off

Turn on this option to enable the dynamic phase

configuration feature. The following ports are created:

•

phasecounterselect[2..0]

•

phaseupdown

•

phasestep

•

scanclk

•

phasedone

Enable phase shift step

resolution edit

On or Off

Turn on this option to modify the value for Phase shift

step resolution(ps) for each individual PLL output

clock on the Output Clocks page.

By default, the finest phase shift resolution value is 1/8

of the VCO period. If the VCO frequency is at the lower

end of the supported VCO range, the phase shift

resolution might be larger than preferred for your

design. Use this option to fine tune the phase shift step

resolution.

6-4

PLL Dynamic Reconfiguration Parameter Settings

UG-M10CLKPLL

2014.12.15

Altera Corporation

ALTPLL IP Core References