Altera MAX 10 Clocking and PLL User Manual

Page 73

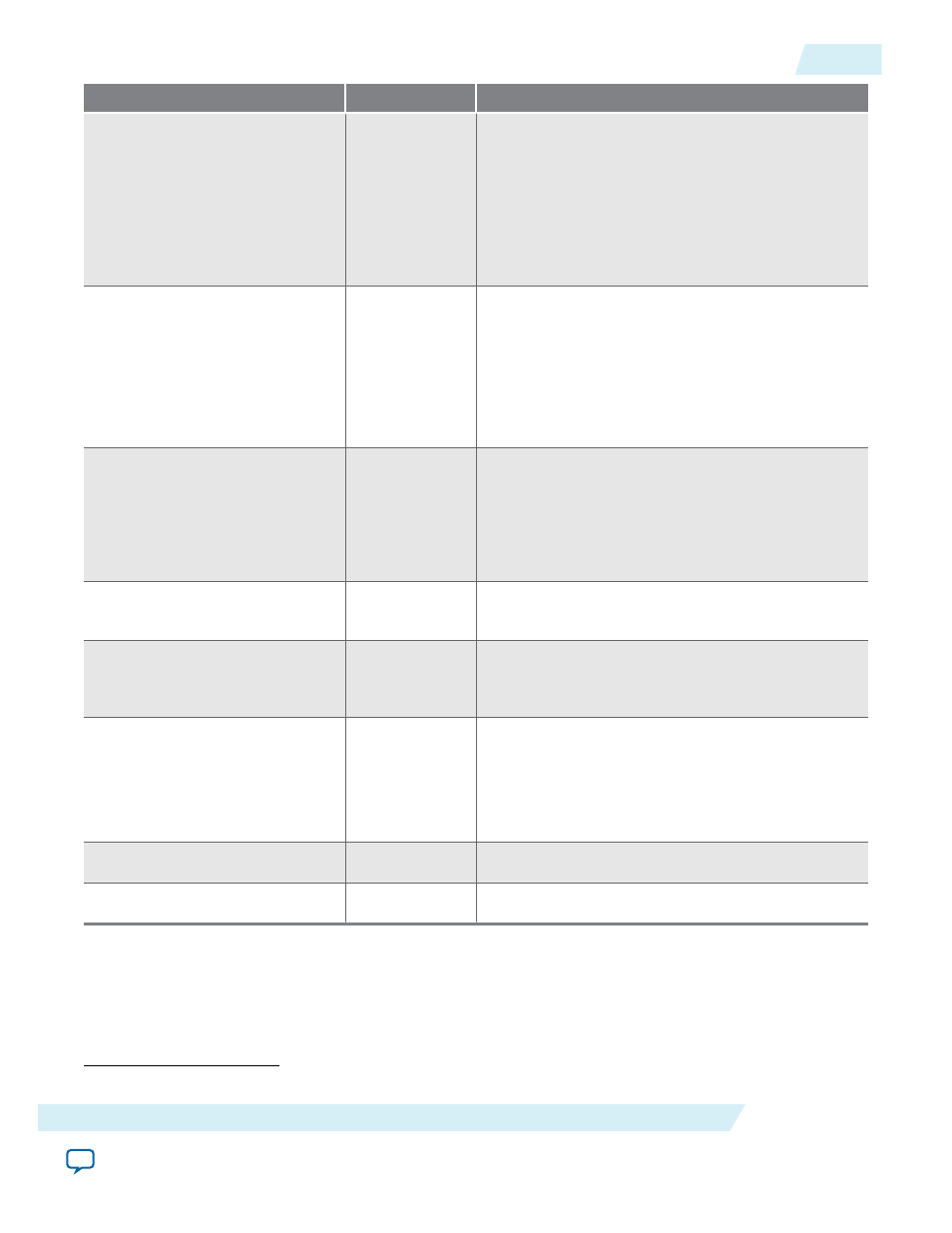

Port Name

(10)

Condition

Description

inclk[]

Required

The clock inputs that drive the clock network.

If more than one

inclk[]

port is created, you must

use the

clkselect

port to specify which clock is

used. The

inclk0

port must always be connected;

connect other clock inputs if switching is necessary.

A dedicated clock pin or PLL output clock can drive

this port.

pfdena

Optional

Enables the phase frequency detector (PFD).

When the PFD is disabled, the PLL continues to

operate regardless of the input clock. Because the

PLL output clock frequency does not change for

some time, you can use the

pfdena

port as a

shutdown or cleanup function when a reliable input

clock is no longer available.

phasecounterselect[]

Optional

Specifies counter select. You can use the

phasecounterselect[2..0]

bits to select either the

M

or one of the

C

counters for phase adjustment.

One address map to select all

C

counters. This signal

is registered in the PLL on the rising edge of

SCANCLK

.

phasestep

Optional

Specifies dynamic phase shifting. Logic high enables

dynamic phase shifting.

phaseupdown

Optional

Specifies dynamic phase shift direction.

1

= UP,

0

=

DOWN. Signal is registered in the PLL on the rising

edge of

SCANCLK

.

scanclk

Optional

Input clock port for the serial scan chain.

Free-running clock from core used in combination

with

PHASESTEP

to enable or disable dynamic phase

shifting. Shared with

SCANCLK

for dynamic reconfi‐

guration.

scanclkena

Optional

Clock enable port for the serial scan chain.

scandata

Optional

Contains the data for the serial scan chain.

(10)

Replace brackets, [], in the port name with integer to get the exact name. For example,

inclk0

and

inclk1

.

UG-M10CLKPLL

2014.12.15

ALTPLL Ports and Signals

6-7

ALTPLL IP Core References

Altera Corporation