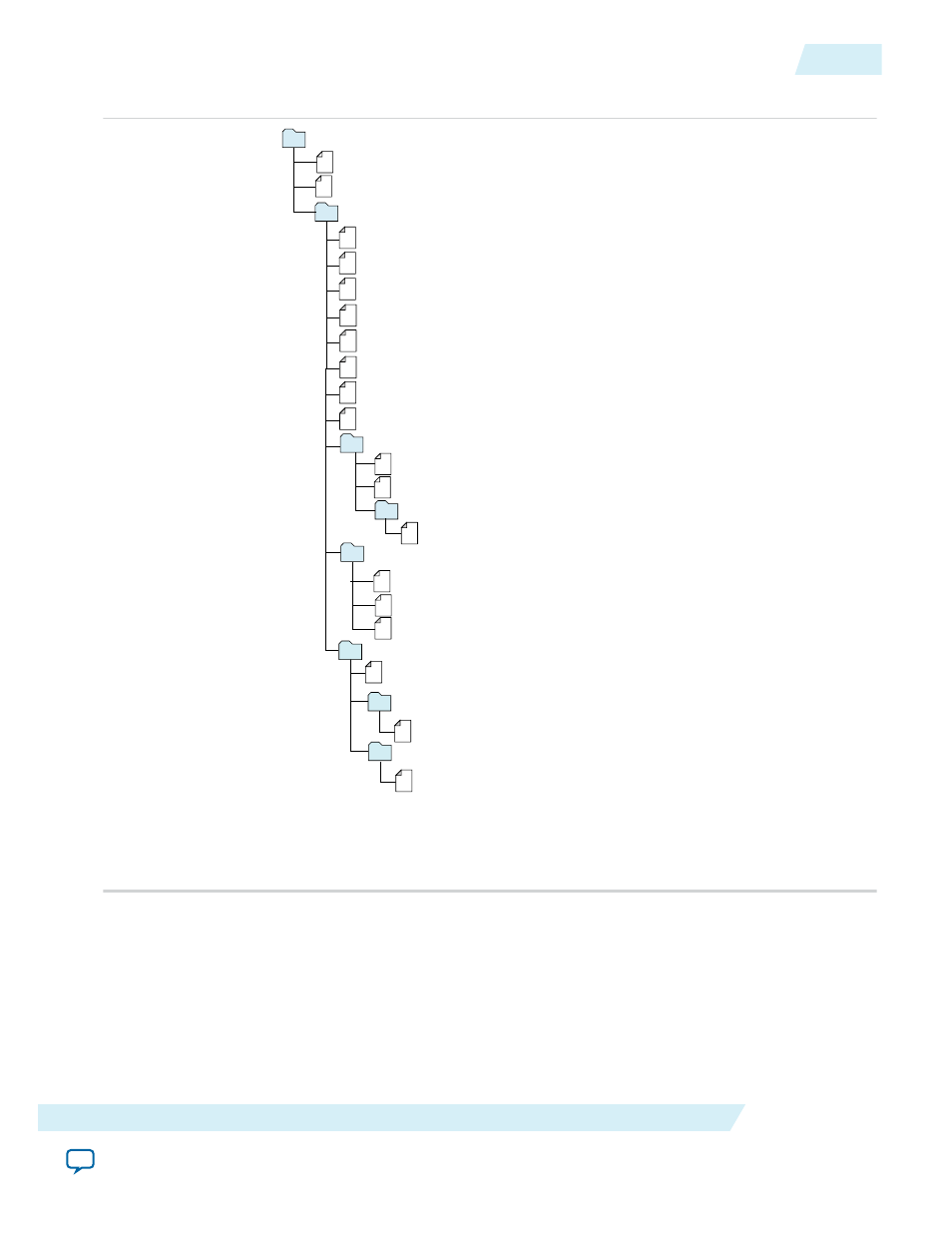

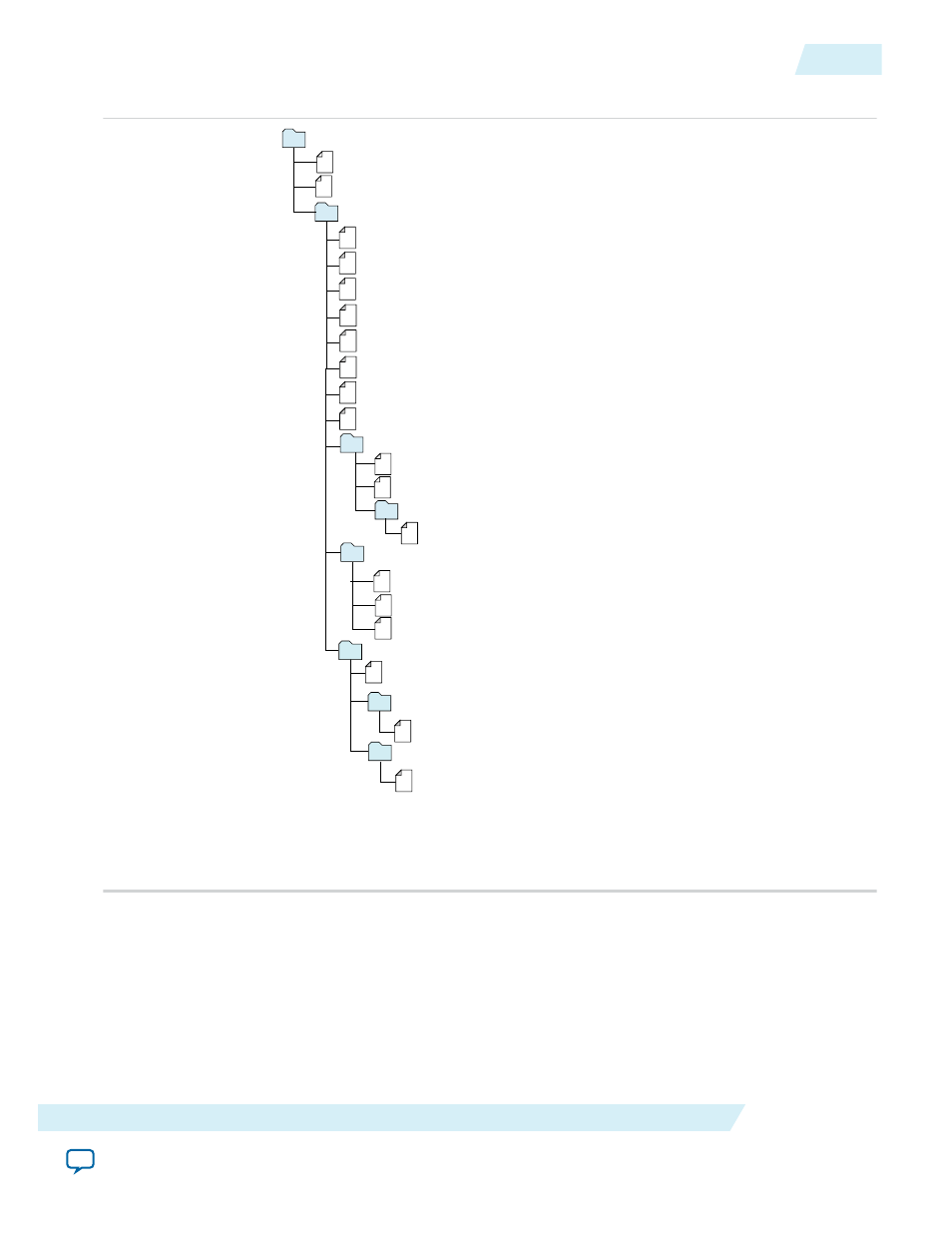

Figure 4-3: IP Core Generated Files

Notes:

1. If supported and enabled for your IP variation

2. If functional simulation models are generated

_bb.v - Verilog HDL black box EDA synthesis file

_inst.v or .vhd - Sample instantiation template

synthesis - IP synthesis files

.qip - Lists files for synthesis

testbench - Simulation testbench files

1

- Testbench for supported simulators

.v or .vhd - Top-level IP variation synthesis file

simulation - IP simulation files

.sip - NativeLink simulation integration file

- Simulator setup scripts

- IP core variation files

.qip or .qsys - System or IP integration file

_generation.rpt - IP generation report

.bsf - Block symbol schematic file

.ppf - XML I/O pin information file

.spd - Combines individual simulation startup scripts

1

.html - Contains memory map

.sopcinfo - Software tool-chain integration file

_syn.v or .vhd - Timing & resource estimation netlist 1

.debuginfo - Lists files for synthesis

.v, .vhd, .vo, .vho - HDL or IPFS models

2

_tb - Testbench for supported simulators

_tb.v or .vhd - Top-level HDL testbench file

ALTPLL IP Core

The ALTPLL IP core specifies the PLL circuitry. You can use this IP core to configure the PLL types,

operation modes, and advanced features of the PLL.

UG-M10CLKPLL

2015.05.04

ALTPLL IP Core

4-5

MAX 10 Clocking and PLL Implementation Guides

Altera Corporation

Send Feedback