Altera MAX 10 Clocking and PLL User Manual

Page 81

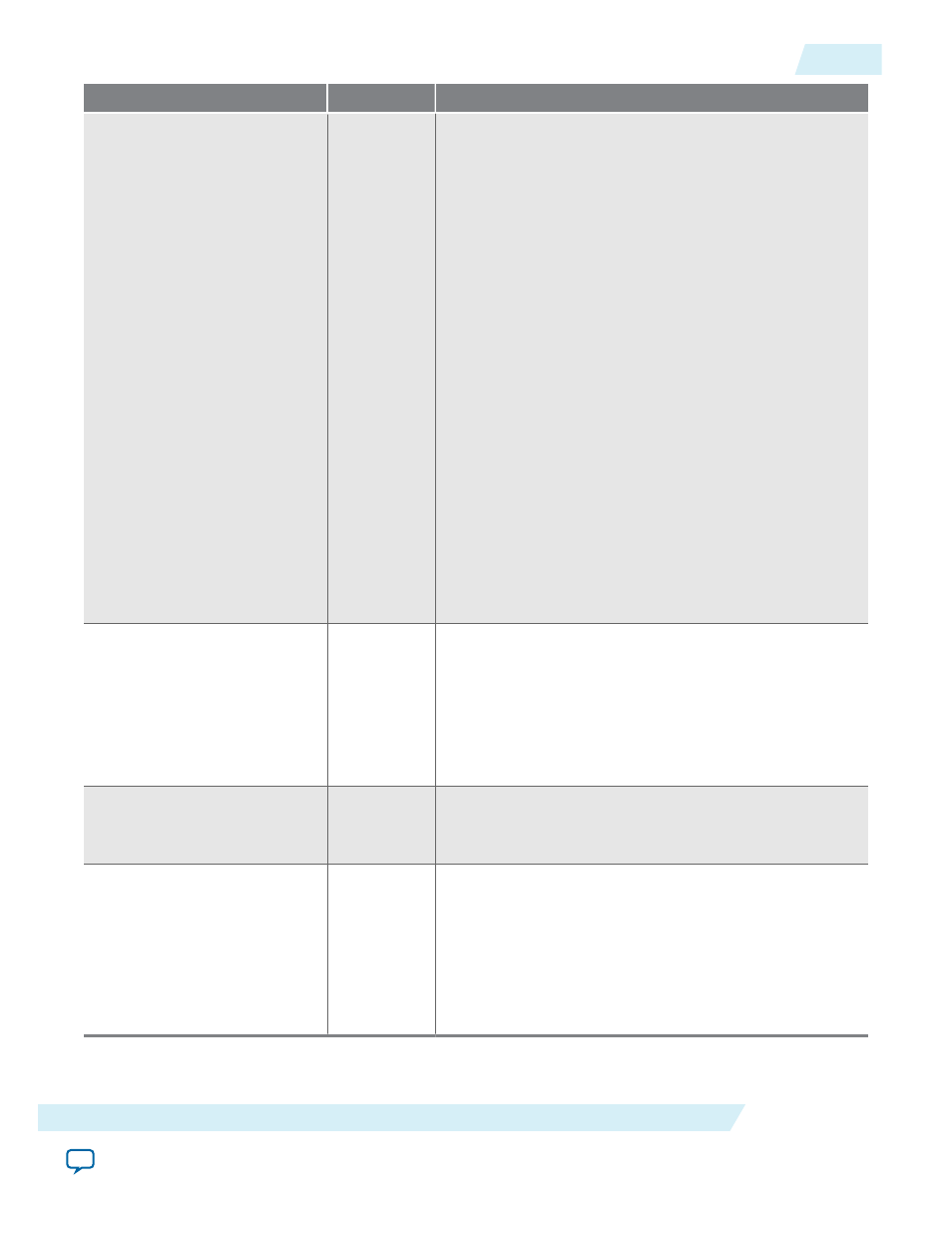

Port Name

Condition

Description

reconfig

Required

Specifies that the PLL should be reconfigured with the

PLL settings specified in the current cache.

When asserted, the

reconfig

signal indicates that the PLL

should be reconfigured with the values in the cache. The

reconfig

signal is sampled at the rising clock edge. If the

reconfig

signal is asserted, the cached settings are loaded

in the PLL. Assert the

reconfig

signal for 1 clock cycle

only to prevent reloading the PLL configuration. The

busy

signal is asserted on the rising clock edge following

the assertion of the

reconfig

signal. While the PLL is

being loaded, the

busy

signal remains asserted. After the

busy

signal is deasserted, the parameter values can be

modified again.

During and after reconfiguration, the scan chain data

cache remains unchanged. This allows you to easily create

a new set of reconfiguration settings using only one

parameter.

If

write_param

has not been asserted since the previous

assertion of

reconfig

, the entire scan chain is shifted in

to the PLL again.

When the

reconfig

signal is asserted, the

busy

signal is

only asserted on the following rising edge of the clock.

The

busy

signal is not asserted on the same clock cycle as

the

reconfig

signal.

pll_areset_in

Optional

Input signal indicating that the PLL should be reset.

When asserted, the

pll_areset_in

signal indicates the

PLL IP core should be reset. This port defaults to 0 if left

unconnected. When using the ALTPLL_RECONFIG IP

core in a design, you cannot reset the PLL in any other

way. You must use this IP core port to manually reset the

PLL.

pll_scandone

Optional

Input port for the ALTPLL_RECONFIG IP core. This

port is driven by the PLL's

scandone

output signal and

determines when the PLL is reconfigured.

pll_scandataout

Required

Input port driven by the

scandataout

signal from the

ALTPLL IP core. Use this port to read the current

configuration of the ALTPLL IP core. This input port

holds the ALTPLL scan data output from the dynamically

reconfigurable bits. The

pll_scandataout

port must be

connected to the

scandataout

port of the PLL. The

activity on this port can only be observed when the

reconfig

signal is asserted.

UG-M10CLKPLL

2015.05.04

ALTPLL_RECONFIG Ports and Signals

7-5

ALTPLL_RECONFIG IP Core References

Altera Corporation