Global clock network power down, Global clock network power down -6 – Altera MAX 10 Clocking and PLL User Manual

Page 12

Each PLL generates five clock outputs through the

c[4..0]

counters. Two of these clocks can drive the

GCLK through a clock control block.

From the Clock Control Block Inputs table, only the following inputs can drive into any given clock

control block:

• Two dedicated clock input pins

• Two PLL counter outputs

• One

DPCLK

pin

• One source from internal logic

The output from the clock control block in turn feeds the corresponding GCLK. The GCLK can drive the

PLL input if the clock control block inputs are outputs of another PLL or dedicated clock input pins.

Normal I/O pins cannot drive the PLL input clock port.

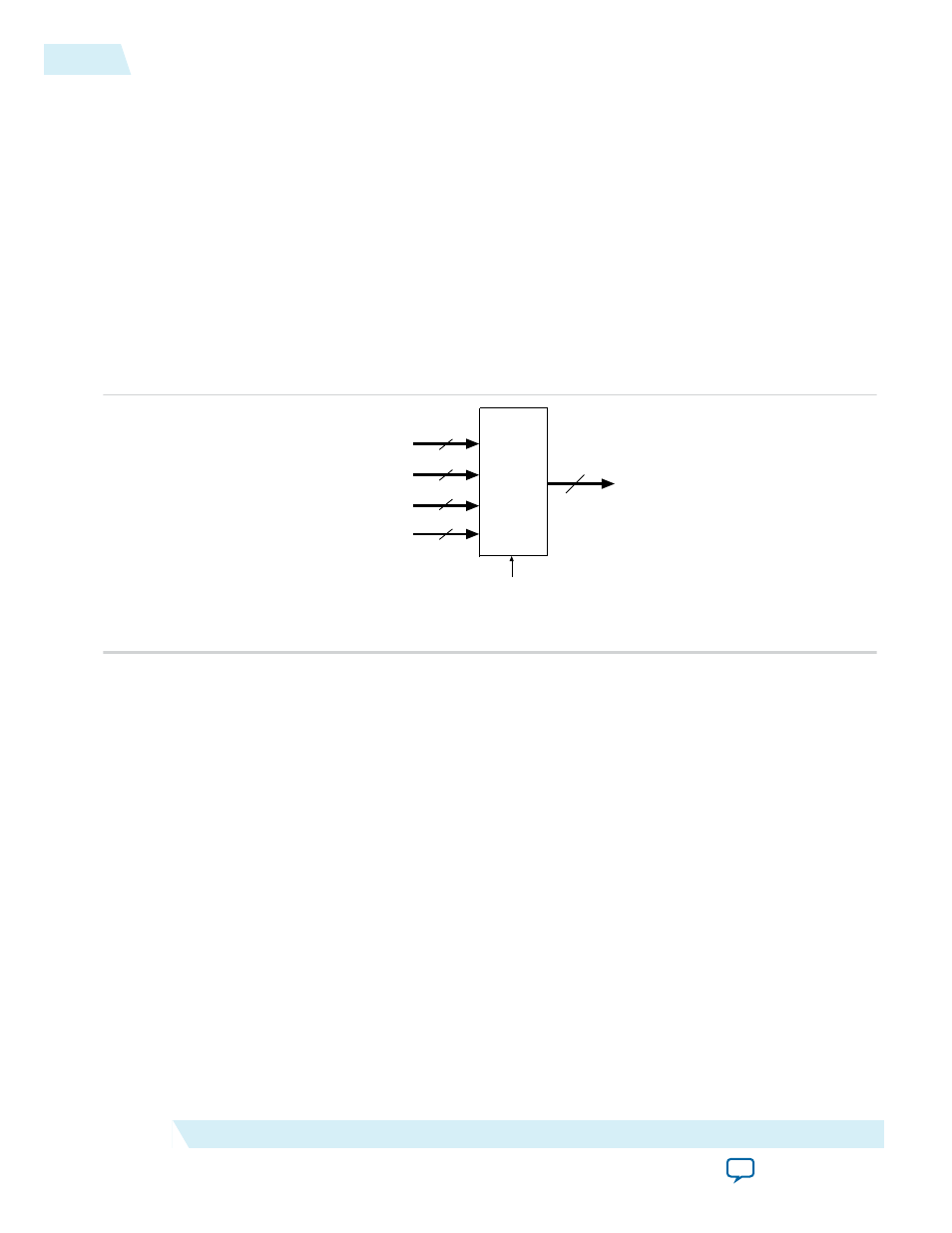

Figure 2-4: Clock Control Block on Each Side of the Device

5

GCLK

Clock Input Pins

4

DPCLK

Internal Logic

Clock

Control

Block

5

PLL Outputs

5

4

Five Clock Control

Blocks on Each Side

of the Device

Out of these five inputs to any clock control block, the two clock input pins and two PLL outputs are

dynamically selected to feed a GCLK. The clock control block supports static selection of the signal from

internal logic.

Related Information

•

•

on page 5-2

Global Clock Network Power Down

You can disable the MAX 10 GCLK (power down) by using both static and dynamic approaches. In the

static approach, configuration bits are set in the configuration file generated by the Quartus

®

II software,

which automatically disables unused GCLKs. The dynamic clock enable or disable feature allows internal

logic to control clock enable or disable of the GCLKs.

When a clock network is disabled, all the logic fed by the clock network is in an off-state, reducing the

overall power consumption of the device. This function is independent of the PLL and is applied directly

on the clock network.

You can set the input clock sources and the

clkena

signals for the GCLK multiplexers through the

ALTCLKCTRL IP core parameter editor in the Quartus II software.

2-6

Global Clock Network Power Down

UG-M10CLKPLL

2015.05.04

Altera Corporation

MAX 10 Clocking and PLL Architecture and Features