Altera MAX 10 Clocking and PLL User Manual

Page 79

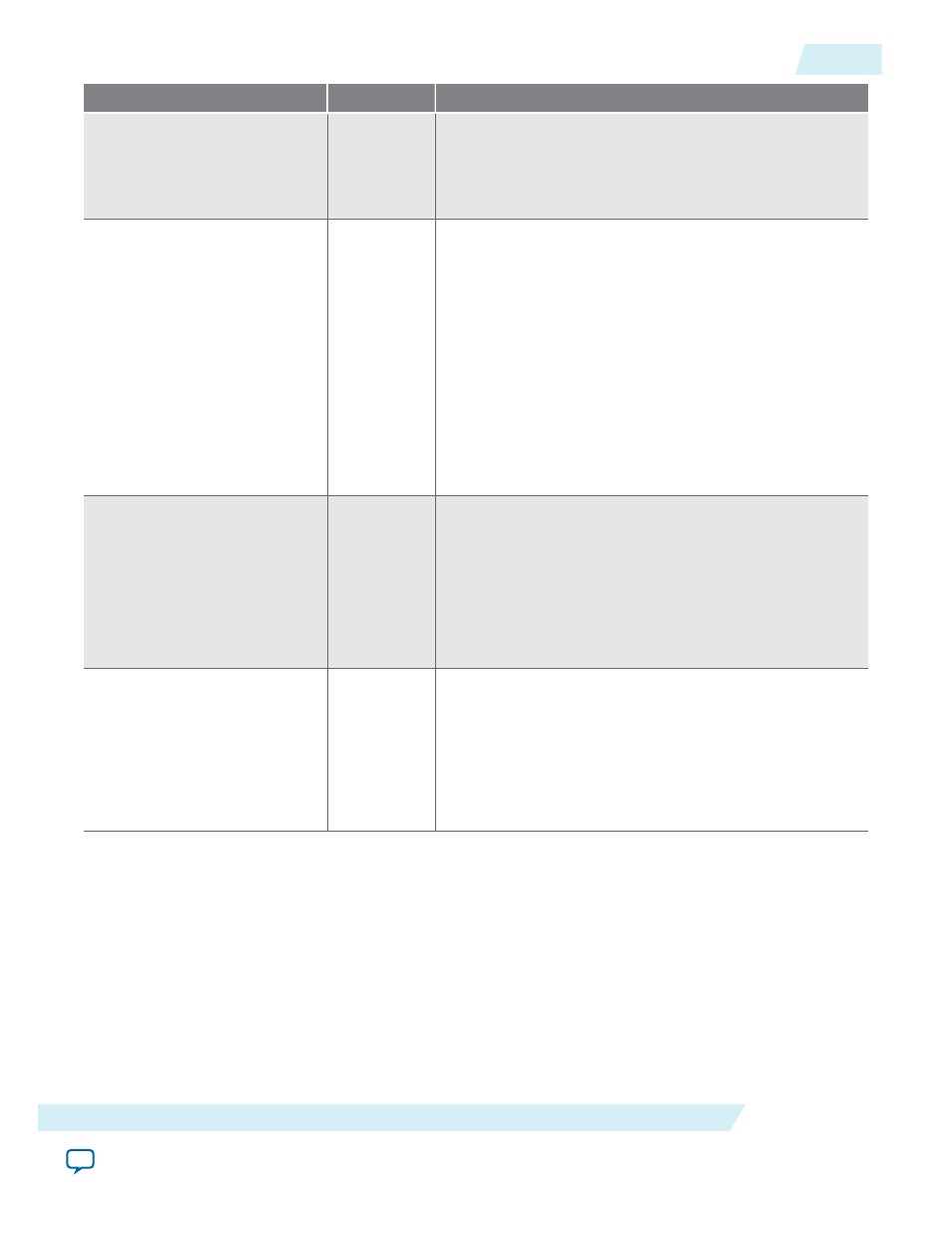

Port Name

Condition

Description

reset

Required

Asynchronous reset input to the IP core.

Altera recommends that you reset this IP core before first

use to guarantee that it is in a valid state. However, it does

power up in the reset state. This port must be connected.

data_in[]

Optional

Data input that provides parameter value when writing

parameters.

This 9-bit input port provides the data to be written to the

scan cache during a write operation. The bit width of the

counter parameter to be written determines the number

of bits of

data_in[]

that are read into the cache.

For example, the low bit count of the

C0

counter is 8-bit

wide, so

data_in[7..0]

is read to the correct cache

location. The bypass mode for the

C0

counter is 1-bit

wide, so

data_in[0]

is read for the value of this

parameter.

If omitted, the default value is 0.

counter_type[]

Optional

Specifies the counter type.

An input port in the form of a 4-bit bus that selects which

counter type should be selected for the corresponding

operation (read, write, or reconfig).

Refer to the

counter_type[3..0]

settings table for the

mapping between the

counter_type

value and the

physical counter to be set.

counter_param[]

Optional

Specifies the parameter for the value specified in the

counter_type

port.

An input port in the form of a 3-bit bus that selects which

parameter for the given counter type should be updated.

The mapping to each parameter type and the

corresponding parameter bit-width are defined in the

counter_param[3..0]

settings table.

UG-M10CLKPLL

2015.05.04

ALTPLL_RECONFIG Ports and Signals

7-3

ALTPLL_RECONFIG IP Core References

Altera Corporation