Output clocks parameter settings, Output clocks parameter settings -5 – Altera MAX 10 Clocking and PLL User Manual

Page 71

Related Information

•

on page 2-20

•

Dynamic Phase Configuration Implementation

Output Clocks Parameter Settings

The Output Clocks page of the ALTPLL parameter editor contains the parameter settings of the clock

output signals. You can configure the

c0

,

c1

,

c2

,

c3

, and

c4

clock output signals of the ALTPLL IP core.

Each option has the following two columns:

• Requested settings—The settings that you want to implement.

• Actual settings—The settings closest values that can be implemented in the PLL circuit to best approxi‐

mate the requested settings.

Use the values in the actual settings column as a guide to adjust the requested settings. If the requested

settings for one of the output clocks cannot be approximated, the ALTPLL IP core parameter editor

produces a warning message at the top of every page.

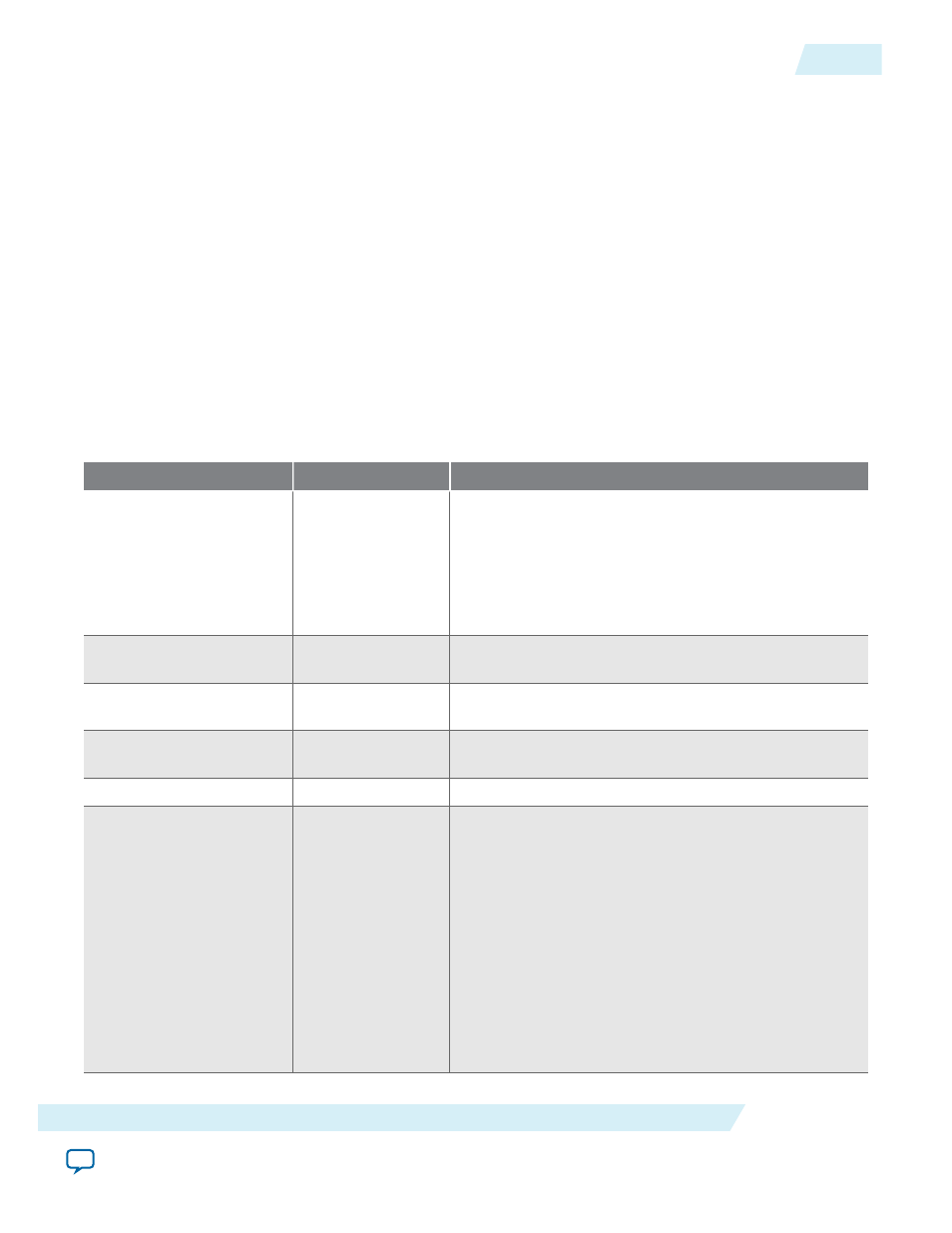

Table 6-6: Output Clocks Parameter Editor Settings

Parameter

Value

Description

Use this clock

On or Off

Turn on this option to generate an output clock port in

your ALTPLL instance.

The output clock port that is to be compensated for is

enabled by default. It cannot be disabled, unless you

select a different output clock port to be compensated

for.

Enter output clock

frequency

—

Specify the frequency of the output clock signal.

Enter output clock

parameters

—

Specify the the output clock parameters instead of the

frequency.

Clock multiplication

factor

—

Specify the clock multiplication factor of the signal.

Clock division factor

—

Specify the clock division factor of the signal.

Clock phase shift

—

Set the programmable phase shift for an output clock

signals.

The smallest phase shift is 1/8 of VCO period. For

degree increments, the maximum step size is 45

degrees. You can set smaller steps using the Clock

multiplication factor and Clock division factor

options.

For example, if the post-scale counter is 32, the smallest

phase shift step is 0.1°. The up and down buttons let

you cycle through phase shift values. Alternatively, you

can enter a number in the phase shift field manually

instead of using the buttons.

UG-M10CLKPLL

2014.12.15

Output Clocks Parameter Settings

6-5

ALTPLL IP Core References

Altera Corporation