Altclkctrl ports and signals, Altclkctrl ports and signals -2 – Altera MAX 10 Clocking and PLL User Manual

Page 65

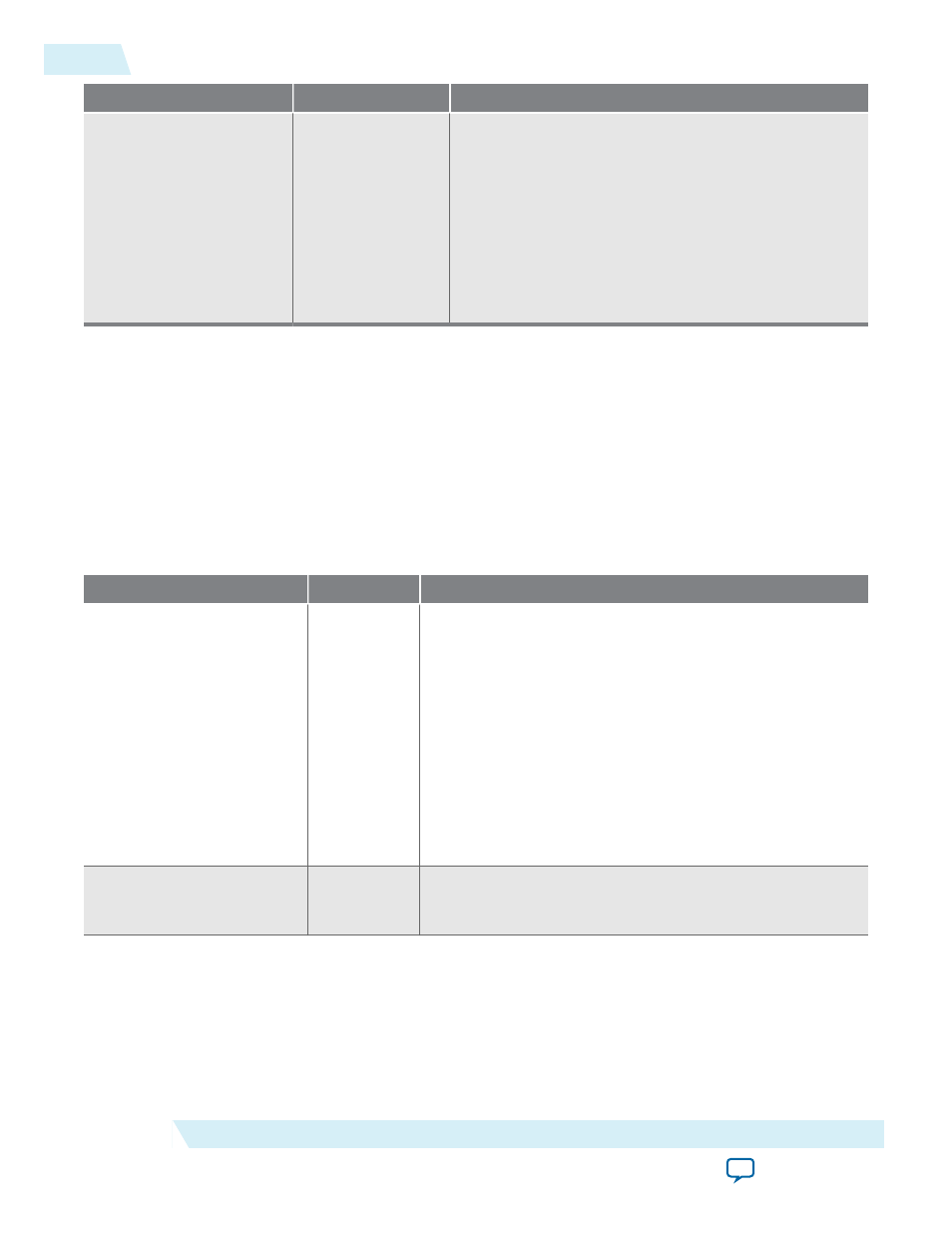

Parameter

Value

Decription

Ensure glitch-free

switchover implementa‐

tion

On or Off

Turn on this option to implement a glitch-free

switchover when you use multiple clock inputs.

You must ensure the currently selected clock is running

before switching to another source. If the selected clock

is not running, the glitch-free switchover implementa‐

tion will not be able to switch to the new clock source.

By default, the

clkselect

port is set to

00

. A clock

must be applied to

inclk0x

for the values on the

clkselect

ports to be read.

Related Information

•

•

Global Clock Network Power Down

on page 2-6

•

on page 2-7

•

Guideline: Clock Enable Signals

on page 3-1

ALTCLKCTRL Ports and Signals

Table 5-2: ALTCLKCTRL Input Ports for MAX 10 Devices

Port Name

Condition

Description

clkselect[]

Optional

Input that dynamically selects the clock source to drive the

clock network that is driven by the clock buffer.

Input port

[1 DOWNTO 0]

wide.

If omitted, the default is GND.

If this signal is connected, only the global clock network can

be driven by this clock control block.

The following list shows the signal selection for the binary

value:

•

00

—

inclk[0]

•

01

—

inclk[1]

ena

Optional

Clock enable of the clock buffer.

If omitted, the default value is V

CC

.

5-2

ALTCLKCTRL Ports and Signals

UG-M10CLKPLL

2015.05.04

Altera Corporation

ALTCLKCTRL IP Core References