Automatic switchover with manual override – Altera MAX 10 Clocking and PLL User Manual

Page 30

When using automatic clock switchover mode, the following requirements must be satisfied:

• Both clock inputs must be running when the FPGA is configured.

• The period of the two clock inputs differ by no more than 20%.

If the current clock input stops toggling while the other clock is also not toggling, switchover is not

initiated and the

clkbad[0..1]

signals are not valid. If both clock inputs do not have the same frequency,

but their period difference is within 20%, the clock sense block detects when a clock stops toggling.

However, the PLL might lose lock after the switchover completes and needs time to relock.

Note: Altera recommends resetting the PLL using the

areset

signal to maintain the phase relationships

between the PLL input and output clocks when using clock switchover.

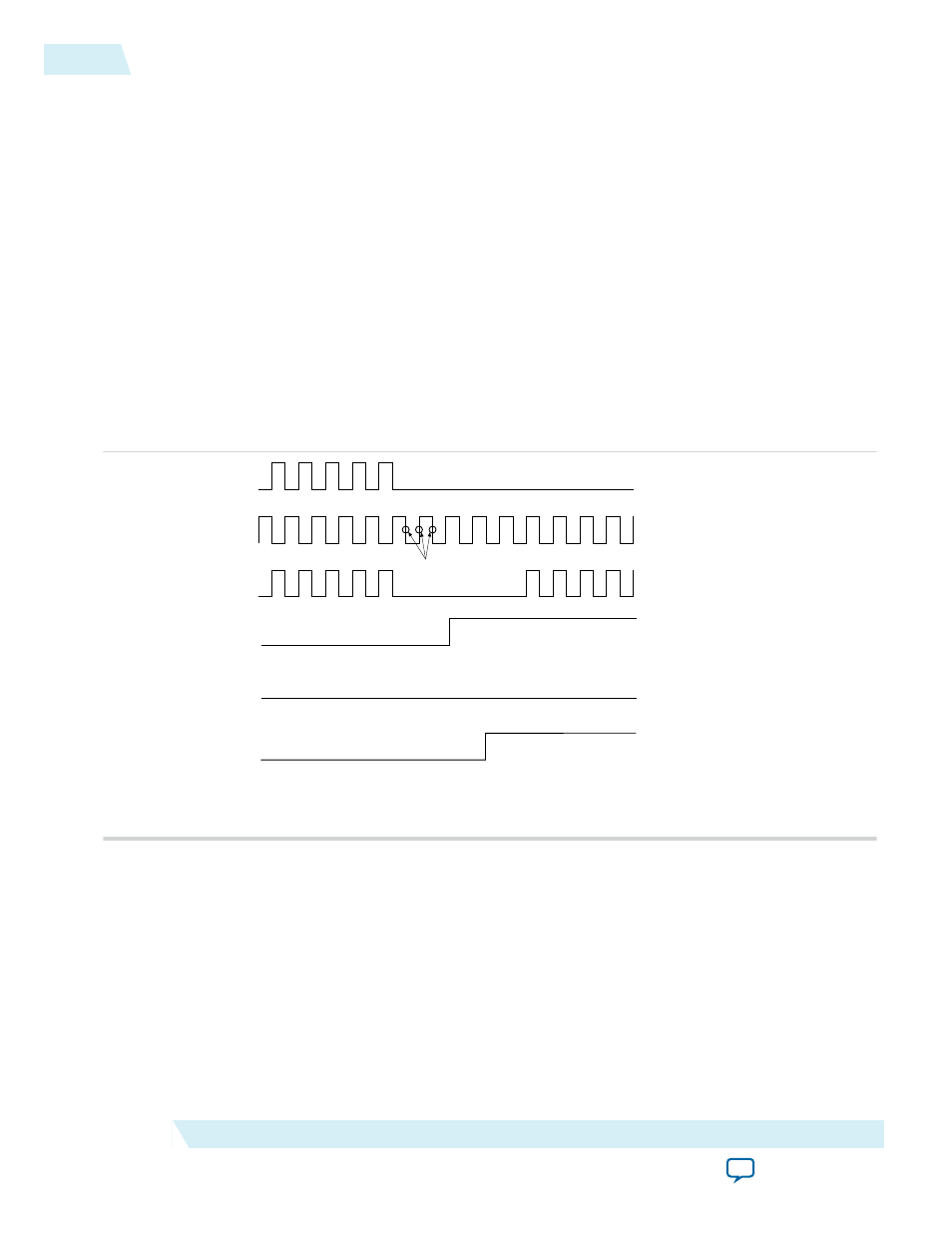

Figure 2-21: Example of Automatic Switchover After Loss of Clock Detection

This figure shows an example waveform of the switchover feature in automatic switchover mode. In this

example, the

inclk0

signal remains low. After the

inclk0

signal remains low for approximately two clock

cycles, the clock sense circuitry drives the

clkbad[0]

signal high. Since the reference clock signal is not

toggling, the switchover state machine controls the multiplexer through the

clksw

signal to switch to the

backup clock,

inclk1

.

inclk0

inclk1

muxout

clkbad0

clkbad1

(1)

activeclock

Note:

(1) Switchover is enabled on the falling edge of inclk0 or inclk1, depending on which clock is available. In this figure,

switchover is enabled on the falling edge of inclk1.

Automatic Switchover with Manual Override

In automatic switchover with manual override mode, you can use the

clkswitch

signal for user- or

system-controlled switch conditions. You can use this mode for same-frequency switchover, or to switch

between inputs of different frequencies.

For example, if

inclk0

is 66 MHz and

inclk1

is 200 MHz, you must control the switchover using the

clkswitch

signal. The automatic clock sense circuitry cannot monitor clock input (

inclk0

and

inclk1

)

frequencies with a frequency difference of more than 20%.

This feature is useful when clock sources originate from multiple cards on the backplane, requiring a

system-controlled switchover between frequencies of operation.

2-24

Automatic Switchover with Manual Override

UG-M10CLKPLL

2015.05.04

Altera Corporation

MAX 10 Clocking and PLL Architecture and Features