Ds4830a user’s guide, Transmitting byte receiving byte, Receiving slave address – Maxim Integrated DS4830A Optical Microcontroller User Manual

Page 96

DS4830A User’s Guide

96

Matched Slave Address

CUR_SLA.SLA[3:0]

I2CSLA_S

1

I2CSLA2_S

2

I2CSLA3_S

4

I2CSLA4_S

8

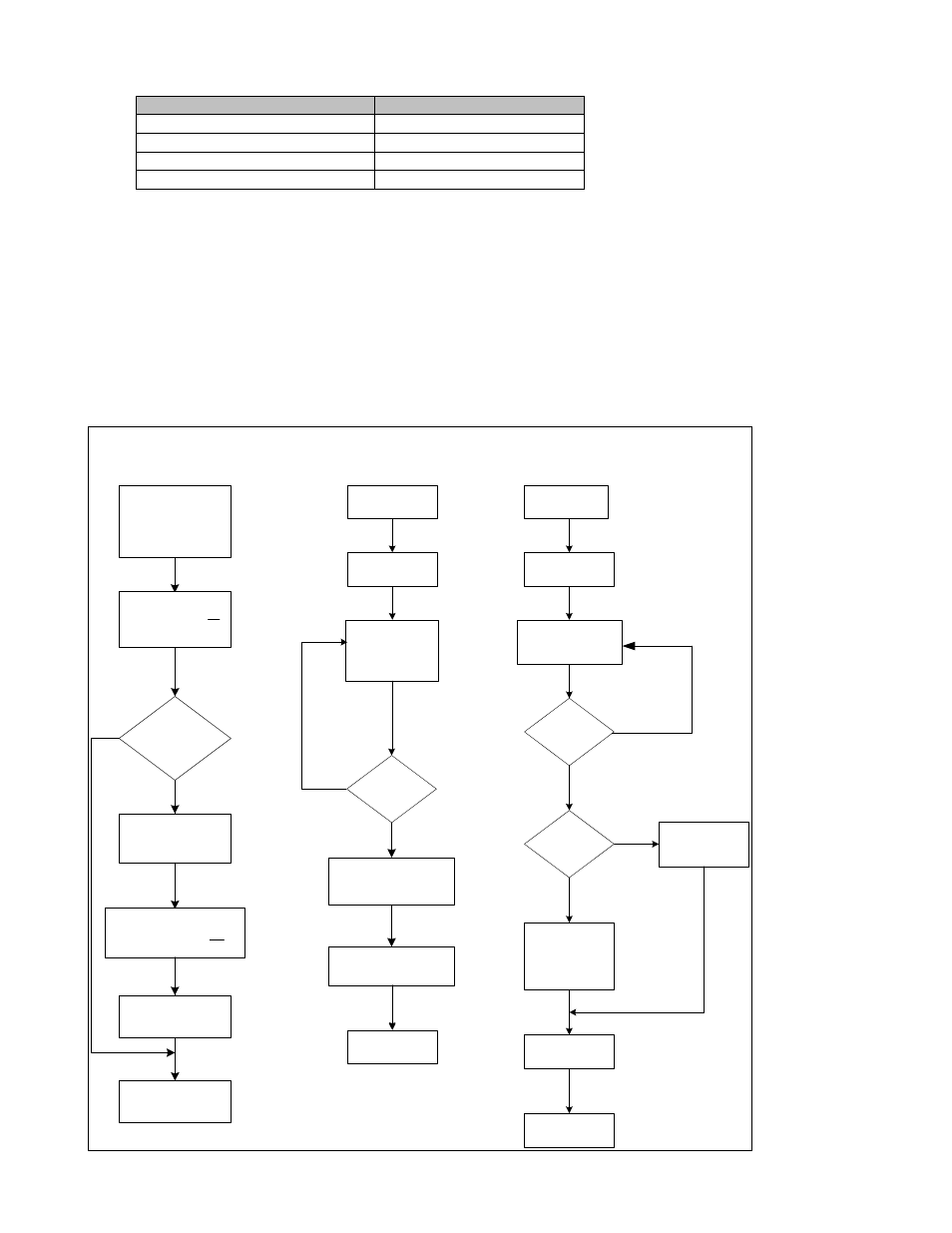

• Clears the I2CBUSY flag.

Upon completion of the slave data byte (7 bits of slave address + R/

W bit + ACK/NACK), the I

2

C slave controller

enters one of the following three states.

• Data Transmit: The slave address matched and the R/

W bit is ‘1’. The host is now expecting data from the

DS4830A. The I

2

C slave controller retains control of the SDA line so data can be transmitted to the host. The

host can start clocking data from the slave at any time.

• Data Receive: The slave address is matched and the R/

W bit is ‘0’. The host wants to write data to the I

2

C

slave. After sending the ACK/NACK bit, the DS4830A releases SDA and is ready to receive a byte of data.

• Wait for START/STOP: The received slave address did not match any enabled slave addresses. The I

2

C

controller enters idle state and waits for the next START or STOP condition.

Transmitting

Byte

Receiving

Byte

Y

Receive

Addr[6:0] + R/W

Match

I2CSLA_S[7:1]

?

Transmit

I2CACK

I2CBUSY=0

N

I2CAMI=1

Set

I2CMODE

According to R/W

Detect START

I2CSRI=1

I2CBUS=1

I2CBUSY=1

I2CNACKI =

ACKNOWLEDGE

Transmit Shift

Register Byte,

MSB First

N

Y

I2CBUSY=1

8 Bits

Transmit

?

I2CTXI=1

I2CBUSY=0

Write to

I2CBUF_S

Receive a Bit into

Shift Register

,

MSB first

N

Y

I2CBUSY=1

8 Bits

Received

?

Load Shift

Register into

I2CBUF_S

I2CRXI=1

Send

I2CACK

Y

N

I2CROI=1

Receiver

Full

?

Detect 1

st

SCL

Rising Edge

I2CBUSY=0

Receiving Slave

Address

RECEIVE

ACKNOWLEDGE

Figure 11-2: Slave I

2

C Data Flow