3 – pwm delay register (pwmdlyn) – Maxim Integrated DS4830A Optical Microcontroller User Manual

Page 131

DS4830A User’s Guide

131

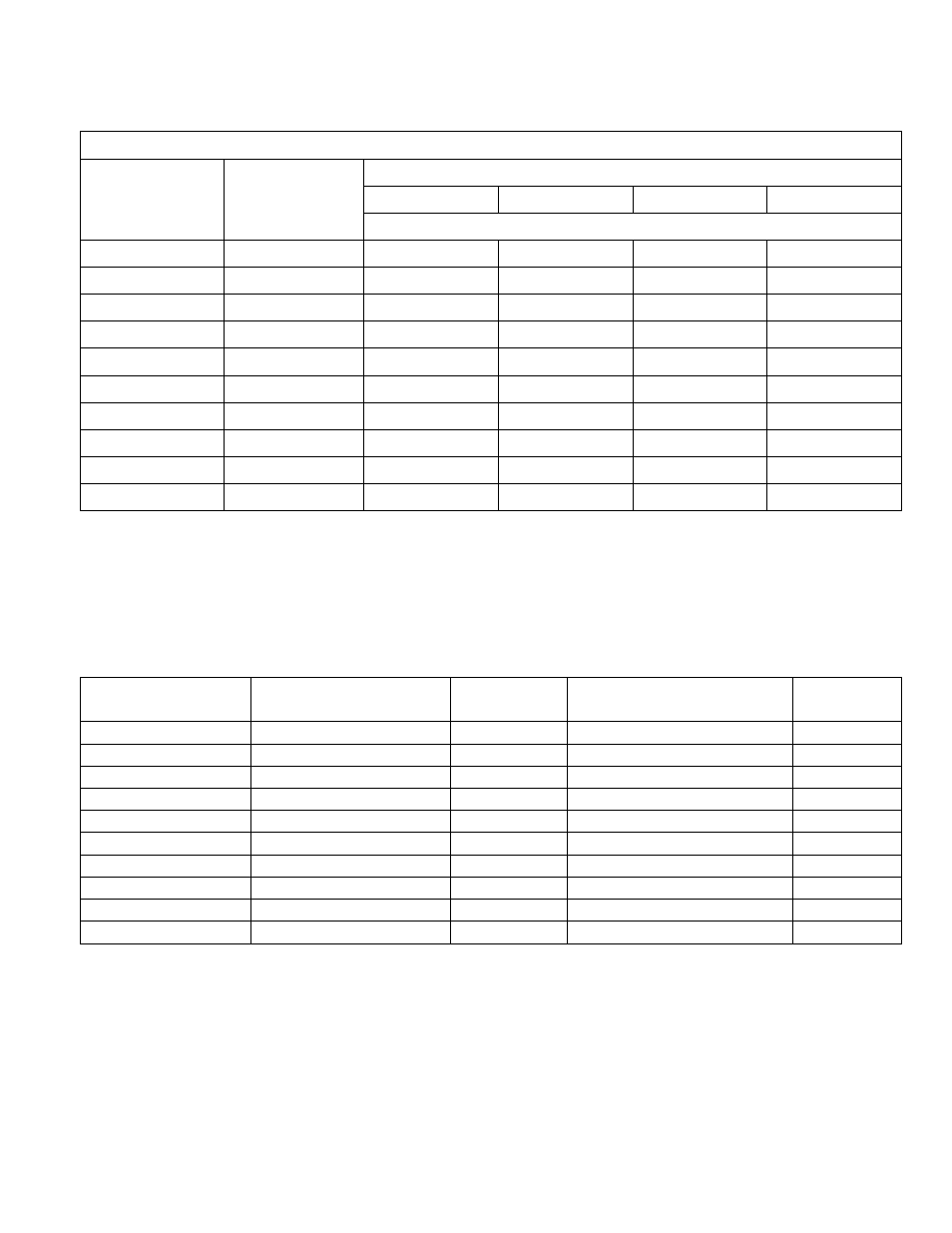

Table 14-4c: Slot Frequencies for Various Resolution and Pulse Spreading with External Clock = 128MHz

Source = External Clock (128MHz)

Resolution

Frame

Frequency (Hz)

Pulse Spreading (PS[1:0])

00

01

10

11

Slot Frequency (Hz)

7

1000000

1000000

1000000

1000000

1000000

8

500000

500000

500000

500000

1000000

9

250000

250000

250000

500000

1000000

10

125000

125000

250000

500000

1000000

11

62500

125000

250000

500000

1000000

12

31250

125000

250000

500000

1000000

13

15625

125000

250000

500000

1000000

14

7812.5

125000

250000

500000

1000000

15

3906.25

125000

250000

500000

1000000

16

1953.125

125000

250000

500000

1000000

14.2.2.2 – Alternate PWM Output

Table 14-5 shows the mapping of each PWM Output. The PWM outputs PW0 to PW7 are also multiplexed with the

DAC output pins. The DS4830A provides the option to select these alternate locations for PW0 to PW7 outputs if

PWM functionality is required along with DAC outputs. When the ALT_LOC is set to ‘1’ during PWM configuration for

a PWM output, the PWM output will be available on this alternate pin. See Table 14-3 for details.

Table 14-5: Alternate PWM Output

PWM OUTPUT PIN

DS4830A PIN NUMBER

WHEN ALT_LOC = 0

GPIO PIN

DS4830A PIN NUMBER

WHEN ALT_LOC = 1

GPIO PIN

PW0

32

P0.4

4

P2.0

PW1

33

P0.5

6

P2.1

PW2

34

P6.5

12

P2.2

PW3

35

P1.5

13

P2.3

PW4

36

P1.6

24

P1.0

PW5

37

P1.7

25

P1.3

PW6

38

P6.6

26

P1.1

PW7

40

P2.7

27

P1.2

PW8

30

P0.6

30

P0.6

PW9

29

P0.7

29

P0.7

14.2.3 – PWM DELAY Register (PWMDLYn)

The Delay Register is used to provide a delay when starting the PWM output. By controlling the starting time for each

individual PWM channel, multiphase operation can be achieved.

The number of bits used to program the Delay depends on the resolution programmed in the PWMCFG SFR. For 12

bits of resolution, the Delay is the lower 12 bits of the PWMDATA register. However if only 7 bits of resolution is

selected, only the lower 7 bits are used to control the Delay of the corresponding PWM Channel. For example if 8-bit

resolution is selected, the maximum delay programmed is limited to 255 (only lower 8 bits are considered).

The Delay resolution also depends on the selected Pulse spreading for the corresponding channel. The maximum

delay is scaled correspondingly. With 10 bits of resolution and 4-slot pulse spreading (PS[1:0] = 2), the maximum

delay programmed is limited to 1024/4 = 256.