7 – adc conversion time, Ds4830a user’s guide – Maxim Integrated DS4830A Optical Microcontroller User Manual

Page 52

DS4830A User’s Guide

52

7.1.7 – ADC Conversion Time

The ADC clock is derived from the system clock with a divide ratio defined by the ADC Clock Divider Bits ADCCLK

[2:0] in the ADC Control register (ADCN). Each sample takes 15 ADC clock cycles to complete. Two of the 15 ADC

clock cycles are used for sample acquisition, and the remaining 13 clocks are used for data conversion. The ADC

automatically reads each measurement twice and outputs the average of the two readings. This makes the resulting

time for one complete conversion to be 30 ADC clock cycles. Additionally, 4 core clocks are used in data processing

for each of the two readings.

Knowing this, it is possible to calculate the fastest ADC sample rate. The fastest ADC clock is:

ADC Clock = Core Clock / 8 = 10 MHz / 8 = 1250 kHz = 0.8 µs

One conversion requires 30 ADC Clocks + 8 Core Clocks

Conversion Time = (30 ADC Clocks Time+ 8 Core Clocks Time)

= 30 * 0.8 + 0.8 µs

= 24.8 µs per ADC Conversion

Sample Rate = 40.3 ksps

The ADC has an internal power management system that automatically shuts down the ADC when conversions are

complete by clearing ADCONV to 0. After being shut down, the ADC begins conversions again when the ADCONV

bit is set to 1 again. After ADCONV is set to 1, the ADC requires 20 ADCCLK cycles to setup and power up prior to

beginning the first conversion of the sequence. So the first ADC conversion time is ~40µs at the fastest ADC Clock.

If the quick trip is also enabled and if the ADC controller and the quick trip are sampling the same channel, the ADC

sampling is delayed by two quick trip conversions (3.2µs) to prevent collision.

In applications where extending the acquisition time is desired, the user can make use of the ADC Acquisition

Extension Bits (ADACQ[3:0] in the ADCN register). When the ADC Acquisition Extension is enabled (ADACQEN=1),

the sample is acquired over a prolonged period during the sample acquisition. The extended acquisition time is

determined by ADACQ[3:0]. Table 7-2 shows the extended acquisition time in terms of core clocks at different

ADACQ[3:0] The total acquisition time, ACQ, is two ADC clocks plus the Extended Acquisition Time (ADACQ, as

listed in Table 7-2). Figure 7-4 shows the clocking required for one conversion.

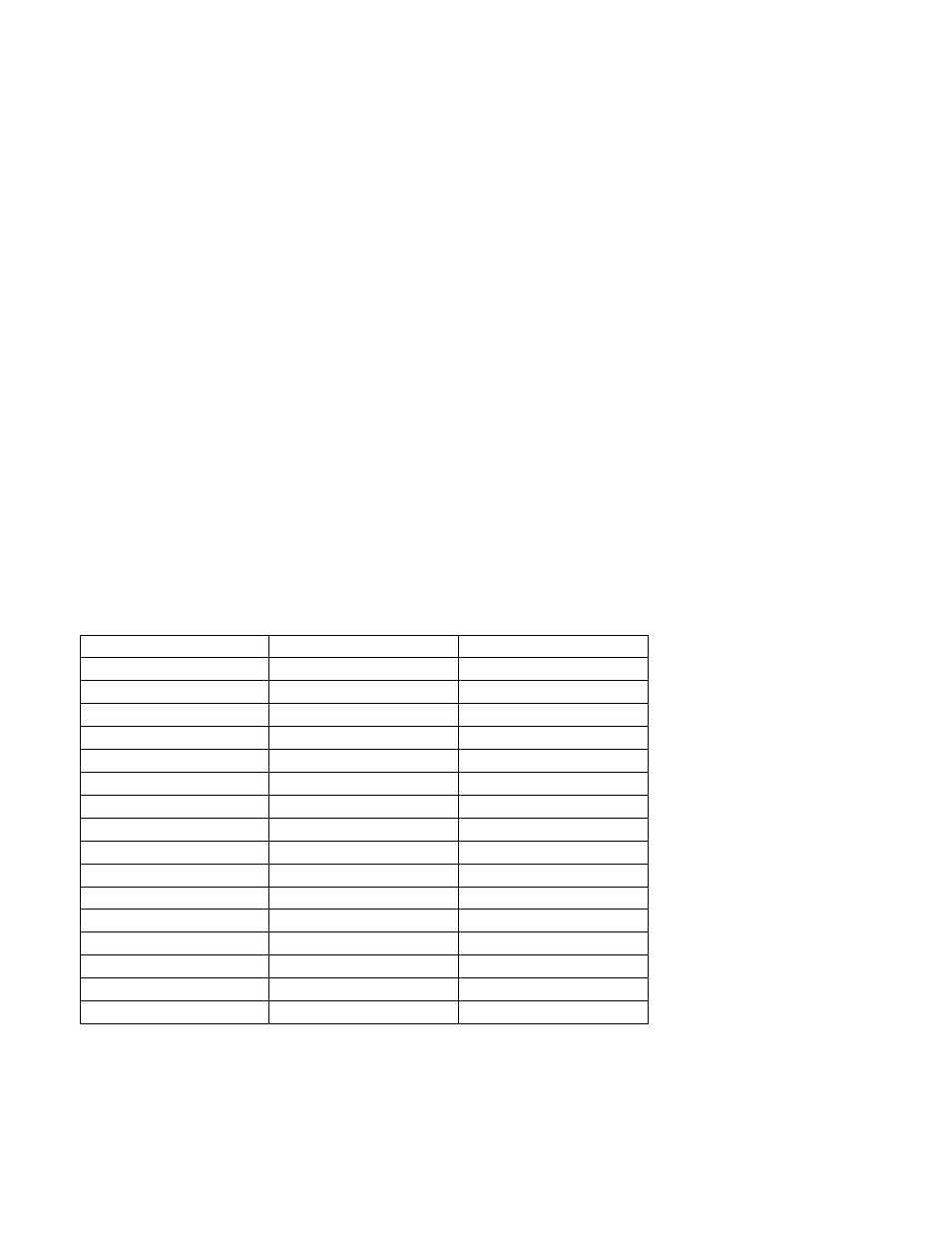

Table 7-2: Extended Acquisition Time in Terms of Core Clock and Time (µs)

ADACQ[3:0]

# of Core Clocks

Time (µs)

0

2

0.2

1

6

0.6

2

14

1.4

3

30

3.0

4

62

6.2

5

126

12.6

6

254

25.4

7

520

52

8

1032

103.2

9

2056

205.6

10

4104

410.4

11

8190

819

12

16382

1638.2

13

32766

3276.6

14

65534

6553.4

15

131070

13107