2 – pwmsync sfr, Ds4830a user’s guide – Maxim Integrated DS4830A Optical Microcontroller User Manual

Page 125

DS4830A User’s Guide

125

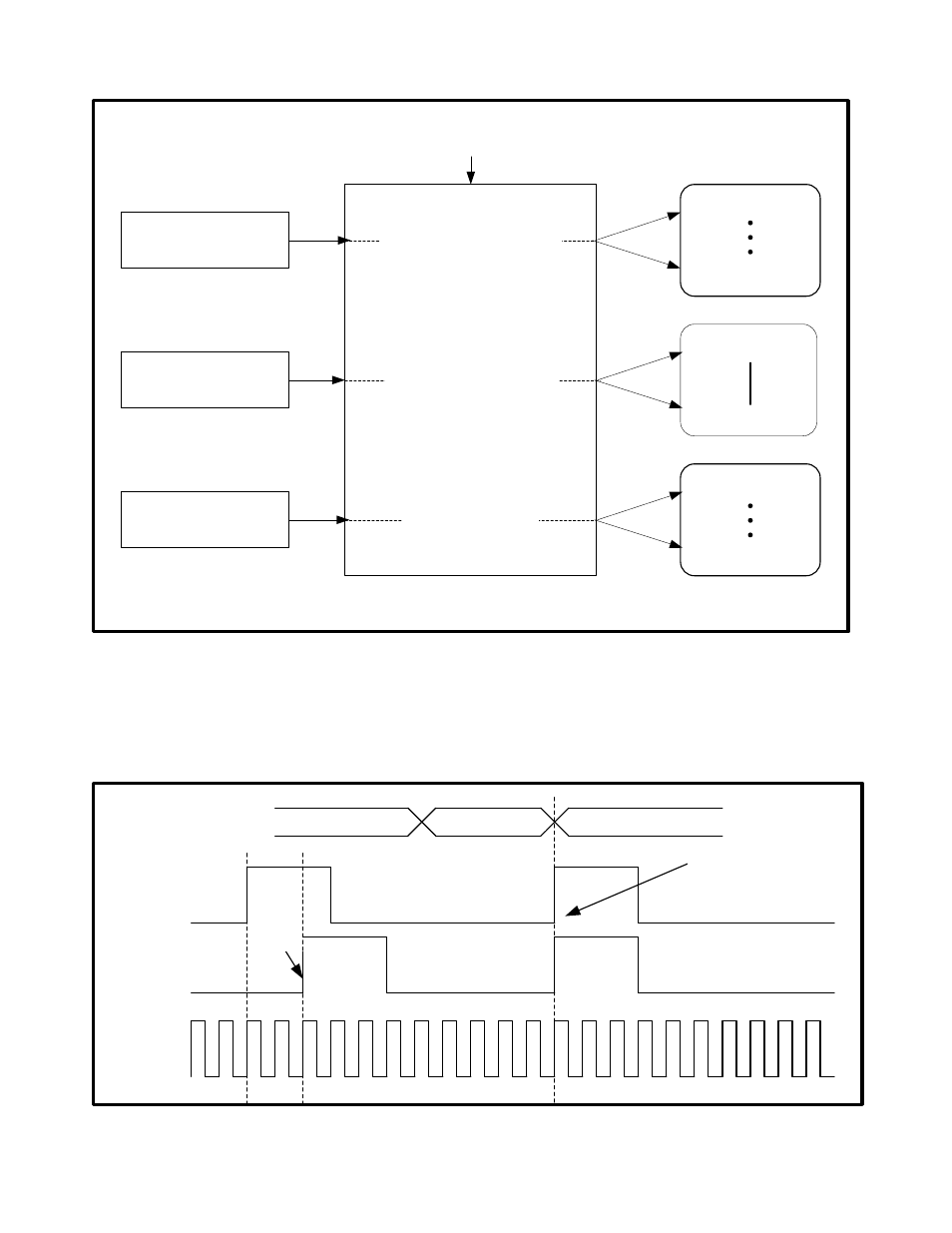

PWMCN.REG_SEL = 00b

PWMCN.PWM_SEL =n

PWMCN.REG_SEL = 01b

PWMCN.PWM_SEL =n

PWMCN.REG_SEL = 1xb

PWMCN.PWM_SEL =n

DCYC0 (Ch0)

DCYC9 (Ch9)

DUTY CYCLE REGISTER

PWMCFG0 (Ch0)

PWMCFG9 (Ch9)

PWM CONFIGURATION

PWMDLY0 (Ch0)

PWMDLY9 (Ch9)

DELAY REGISTER

PWMDATA REGISTER

Note: n = 0 to 9

READ OR WRITE TO PWMDATA

Figure 14-1: Illustration of PWMDATA and PWMCFG SFRs

14.1.2 – PWMSYNC SFR

Different channels can be synchronized using the PWMSYNC register. Doing so effectively brings the channels in phase

by restarting the channels that are to be synchronized, without affecting the PWM operation. The PWM channels to be

synchronized must have the same configurations (Resolution, Pulse Spreading option, Clock source etc.).

The

PWMSYNC register auto clears itself on the next core clock.

Figure 14-2 shows an illustration of the PWMSYNC SFR

operation. See PWM Delay section for more details.

PWM Clock

PWM0

PWM1

Out of

Phase

In Phase

Both PWMs Rstarted

PWMSYNC = 00h

PWMSYNC = 03h

PWMSYNC = 00h

Figure 14-2: PWM Output Synchronization When the Same Delay is Programmed