1 – reference selection, 2 – dac register descriptions, 1 – dac configuration register (daccfg) – Maxim Integrated DS4830A Optical Microcontroller User Manual

Page 46: Ds4830a user’s guide

DS4830A User’s Guide

46

DS4830A IC data sheet). The DAC output voltage is maintained during any type of reset except POR. All DACs,

REFINA and REFINB pins default to GPIO on reset.

6.1.1 – Reference Selection

Each DAC can be independently enabled with 2.5V internal reference or external reference. Each DAC has two bits

in the DAC configuration register (DACCFG) that are used to enable or disable the DAC with either an internal or an

external reference.

Any DAC can be enabled for using the internal reference by writing 10b at the corresponding location in the

DACCFG register. The internal reference automatically powers-down when none of the 8 DACs use it as a reference

source.

The external reference at REFINA (Port2.6) is selected by writing 01b at the corresponding location in the DACCFG

for DAC0-3. The REFINA automatically becomes GPIO when none of the lower 4 DACs (DAC0 to DAC3) use

REFINA as its reference. The external reference at REFINB (Port1.4) is selected by writing 01b at the corresponding

location in the DACCFG register for DAC4-7. The REFINB pin automatically becomes GPIO when none of the upper

4 DACs (DAC4 to DAC7) use REFINB as its reference. The DAC internal or external references can be measured at

the ADC. See ADC section for further detail information.

6.2 – DAC Register Descriptions

The DAC module has total 9 SFR registers. These are DAC Configuration register DACCFG and 8 DAC Data

registers DACDx (DACD0 to DACD7). The DACCFG configures all DACs and the data register DACDx (DACD0-

DACD7) controls the corresponding DAC output voltage. These SFRs are located in module 4.

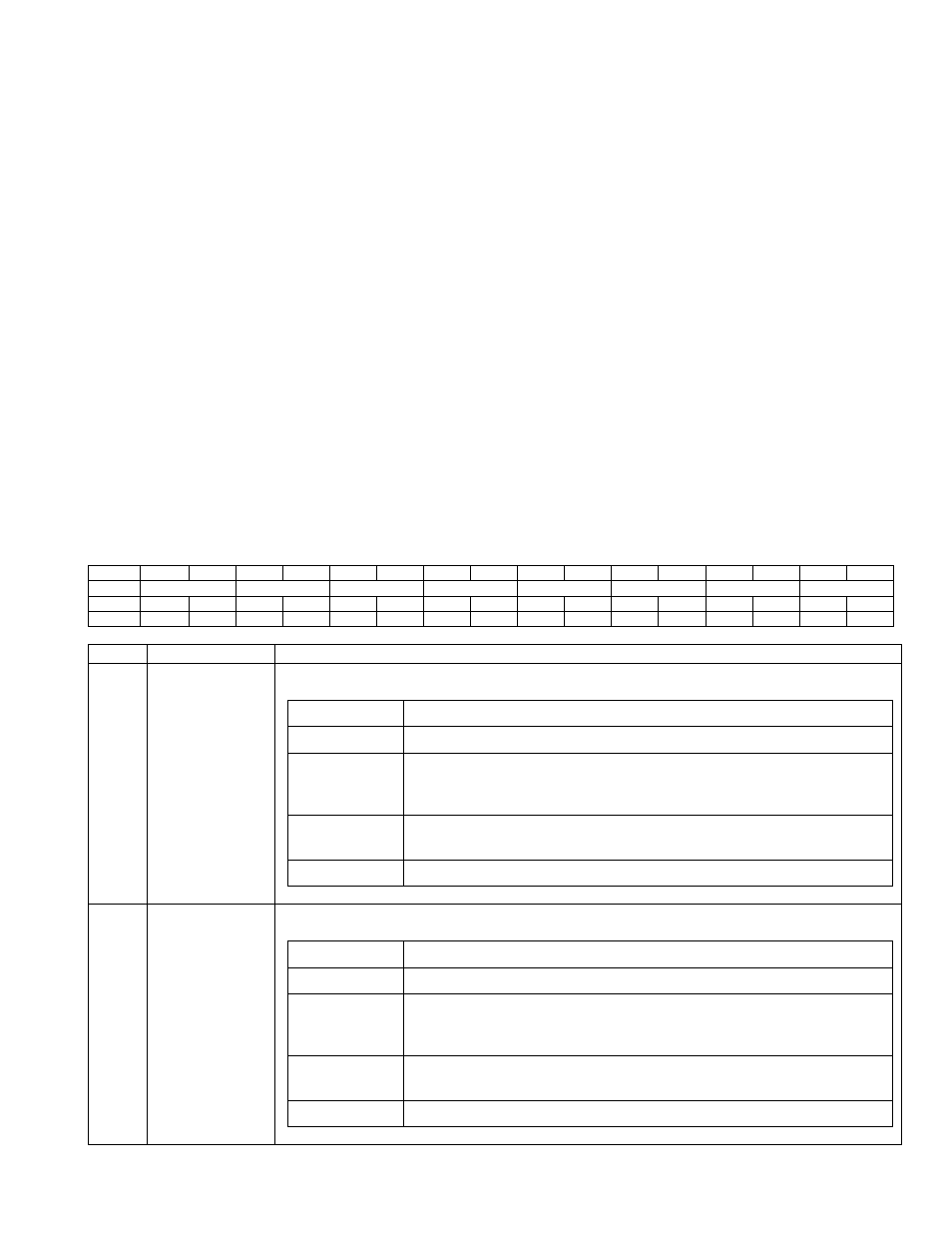

6.2.1 – DAC Configuration Register (DACCFG)

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

DACCFG7[1:0] DACCFG6[1:0] DACCFG5[1:0] DACCFG4[1:0] DACCFG3[1:0] DACCFG2[1:0] DACCFG1[1:0] DACCFG0[1:0]

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

BIT

NAME

DESCRIPTION

15:8

DACCFG7[1:0]

DACCFG6[1:0]

DACCFG5[1:0]

DACCFG4[1:0]

DAC Configuration: These bits configure DAC7-4 and select the DAC reference for

DAC7-4 when the corresponding DAC is enabled.

DACCFGx[1:0]

DACx Control/Reference Select

00

DACx is Disabled and is in power down mode.

01

DACx is enabled and REFINB is selected as the external reference.

To use the external reference, the REFB_CFG bit in the RPCFG

register must be set to ‘1’.

10

DACx is enabled and the 2.5V Internal Reference is selected as the

DAC reference

11

Reserved. (User should not write this value

+

)

PIN 39 is REFINB (Port1.4).

7:0

DACCFG3[1:0]

DACCFG2[1:0]

DACCFG1[1:0]

DACCFG0[1:0]

DAC Configuration: These bits configure DAC3-0 and select the DAC reference for

DAC3-0 when DAC enabled.

DACCFGx[1:0]

DACx Control/Reference Select

00

DACx is Disabled and is in power down mode.

01

DACx is enabled and REFINA is selected as the external reference.

To external reference, the REFA_CFG bit in the RPCFG register

must be set to ‘1’.

10

DACx is enabled and the 2.5V Internal Reference is selected as the

DAC reference

11

Reserved. (User should not write this value

+

)

PIN 31 is REFINA (Port2.6).