2 – watchdog timer reset, 3 – external reset, Ds4830a user’s guide – Maxim Integrated DS4830A Optical Microcontroller User Manual

Page 23

DS4830A User’s Guide

23

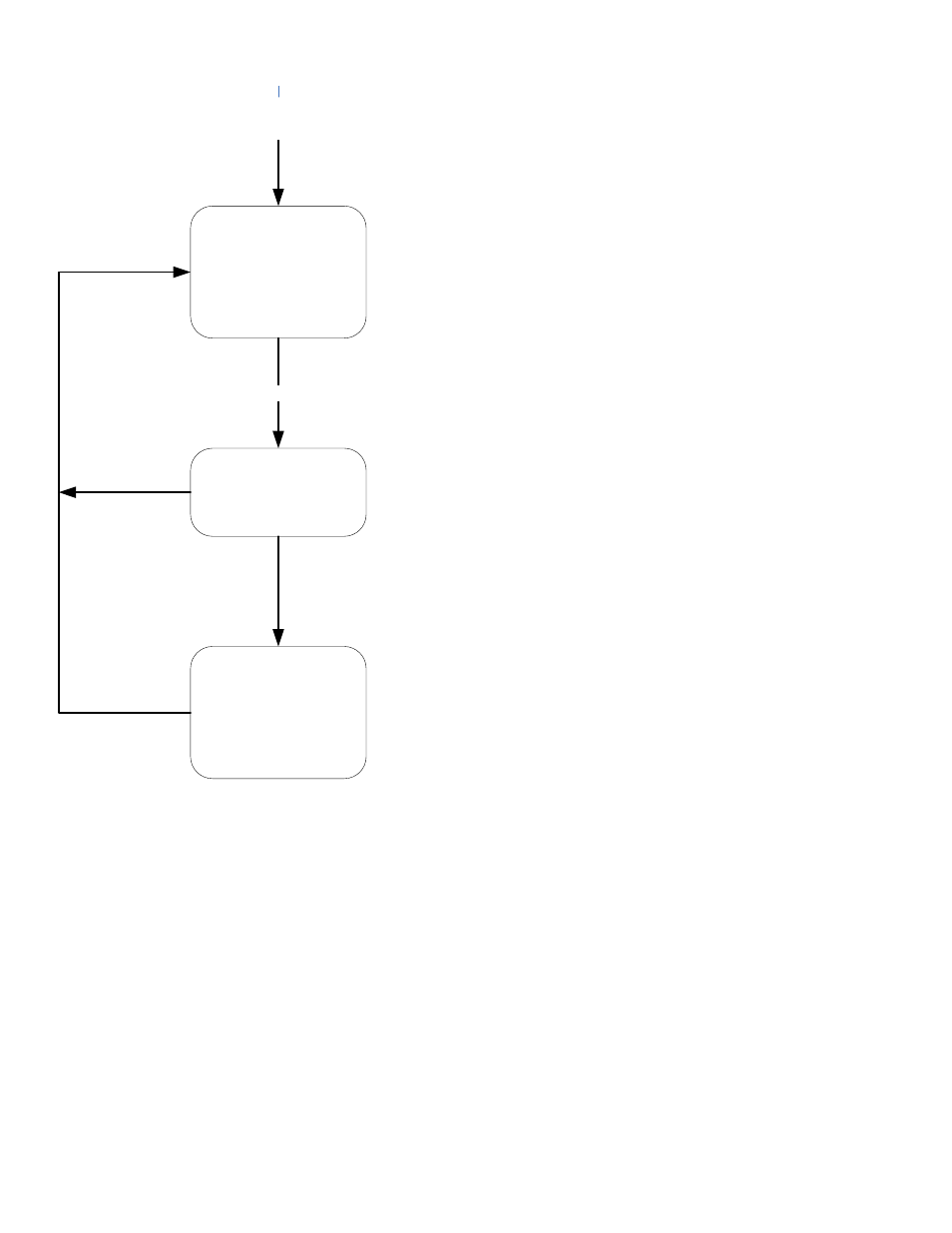

BROWNOUT STATE

CPU DISABLED

ANALOG ACTIVE

SYSTEM CLOCK

STARTUP DELAY

CPU MODE

DIGITAL CORE ON

ANALOG ON

CODE EXECUTION

V

DD

> V

BO

V

DD

< V

BO

POR

V

DD

< V

BO

Figure 2-6: DS4830A State Diagram

2.6.2 – Watchdog Timer Reset

The watchdog timer is a programmable hardware timer that can be used to reset the processor in case a software lockup

or other unrecoverable error occurs. Once the watchdog is enabled, software must reset the watchdog timer periodically.

If the processor does not reset the watchdog timer before it elapses, the watchdog can initiate a reset.

If the watchdog resets the processor, the DS4830A will remain in reset for 12 clock cycles. When a reset occurs due to a

watchdog timeout, the Watchdog Timer Reset Flag (WTRF) in the WDCN register is set to indicate the source of the

reset.

2.6.3 – External Reset

During normal operation, the DS4830A is placed into external reset when the

RST pin is held at logic 0 for at least four

clock cycles. Once the DS4830A enters reset mode, it remains in reset as long as the

RST pin is held at logic 0. After the

RST pin returns to logic 1, the processor exits reset within 12 clock cycles.

An external reset pulse on the

RST pin will reset the DS4830A and return to normal CPU mode operation within 10 clock

cycles.